| Тема 0. Въведение: Развитие на микроелектронните технологии за производство СГИС. Кратка история на 32-битовите микропроцесори (МП) х86 и "ARМ                                                                         | I Luac      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Тема 1. Програмен модел на МП: Понятие за програмен модел. Режими. Региста за обща употреба. Специализирани регистри. Флагове на регистъра за кон на условието (РКУ). Особености. Обзор на програмния модел на други М | ода 1 час   |

| Тема 2. Система от машинни команди: Групи команди. Формат на команди "Операнд 2". Методи за адресация. Ортогоналност на системата команди.                                                                             | ⊥ ∠ часа    |

| Тема 3. Структура на МП: Основни функционални блокове в МП. Вътрешни ши Работа на конвейера.                                                                                                                           | ини. 2 часа |

| Тема 4. Системна магистрала: Сигнали на шините за адреси и данни. Управлява сигнали. Организация на обмена на данни. Видове цикли. Времедиаграми                                                                       | ⊥ ∠ yaca    |

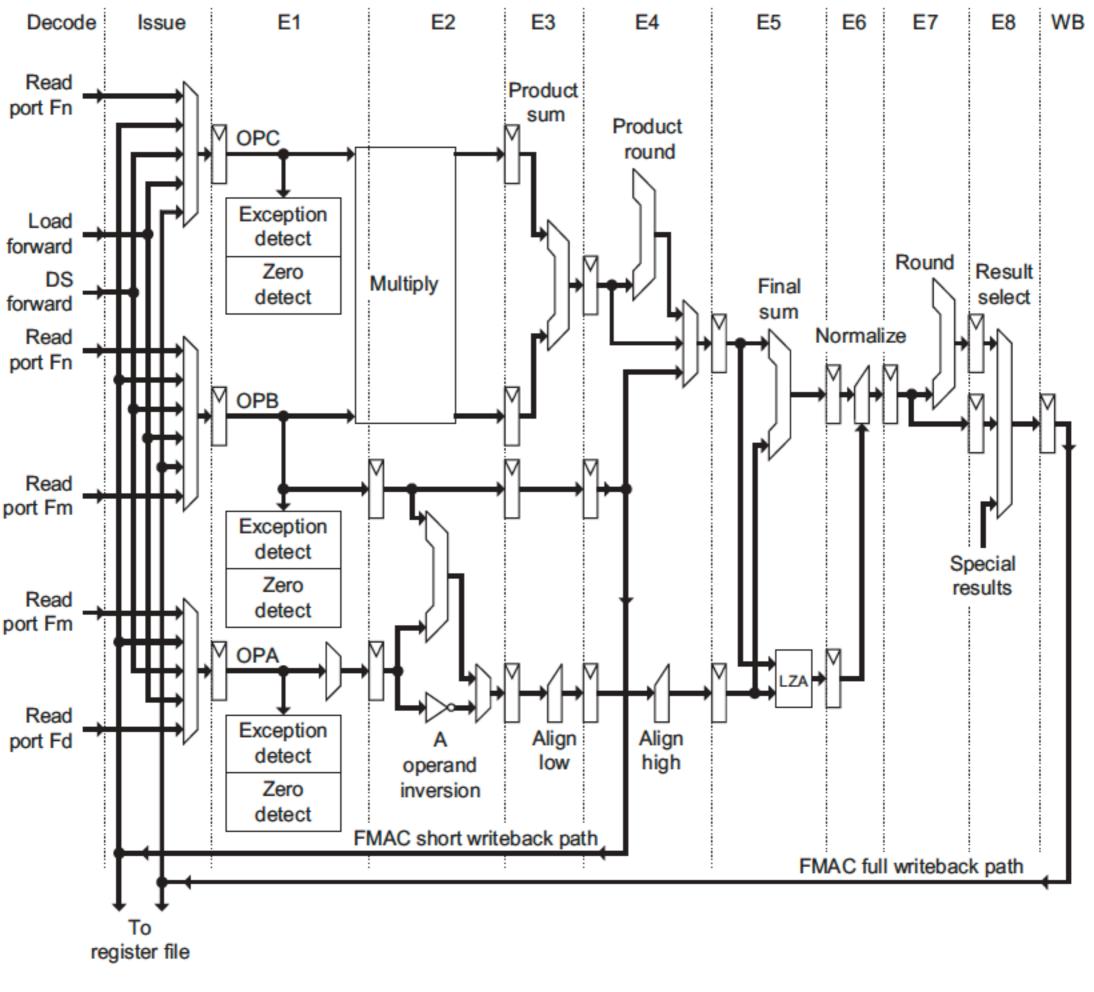

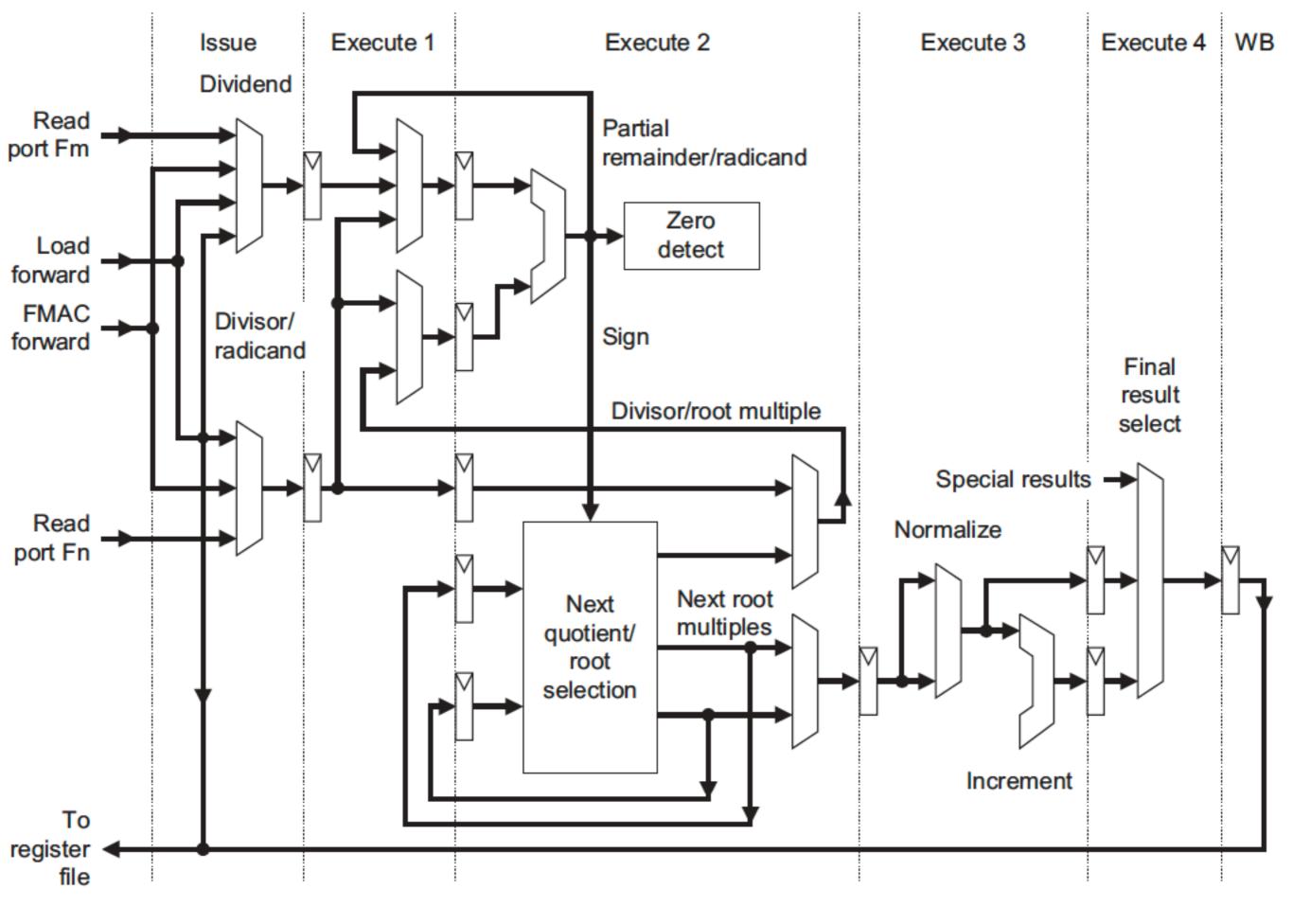

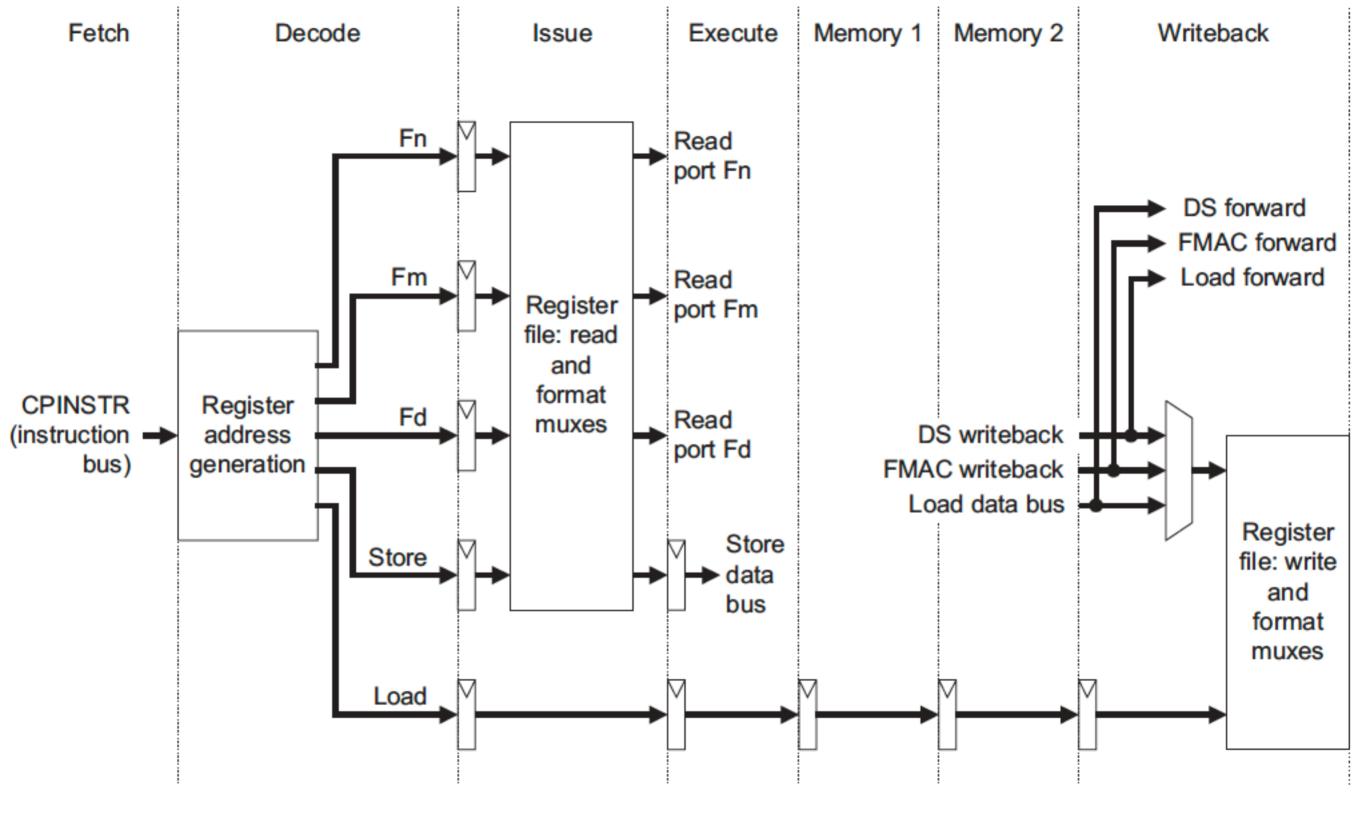

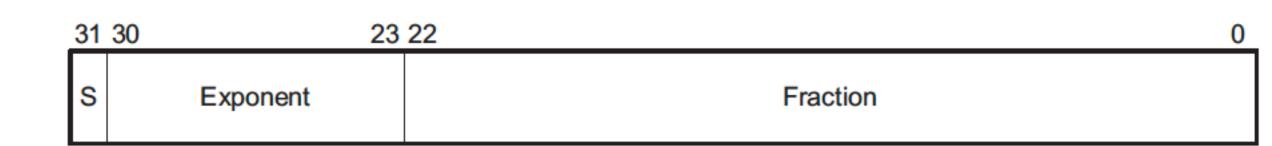

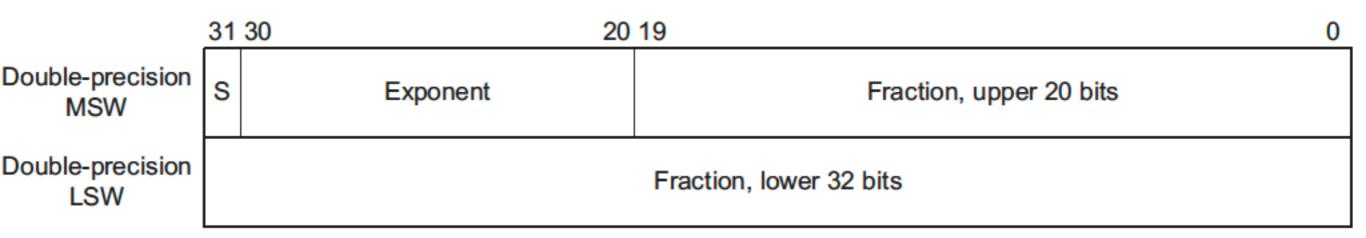

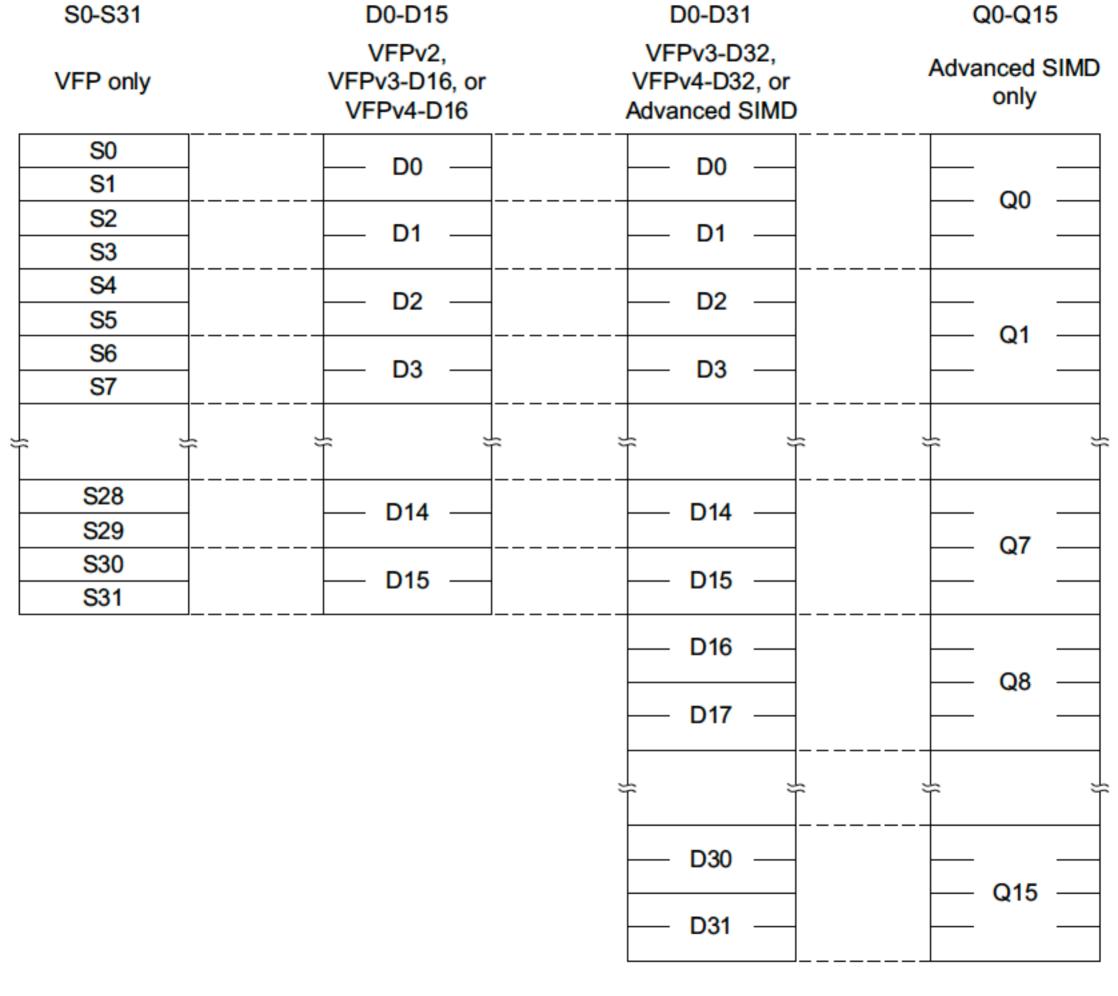

| Тема 5. Устройство за плаваща запетая: Конвейери за умножение и натрупва делене и коренуване и зареждане и съхранение. Режими. Обработка на коректори. Регистров файл. Програмен модел. Команди. Изключения.           |             |

| Тема 6. Изключения и прекъсвания: Изключения. Прекъсвания – видове и връзк режимите на МП. Таблица на векторите на изключенията и прекъсвания Начално установяване на МП.                                              |             |

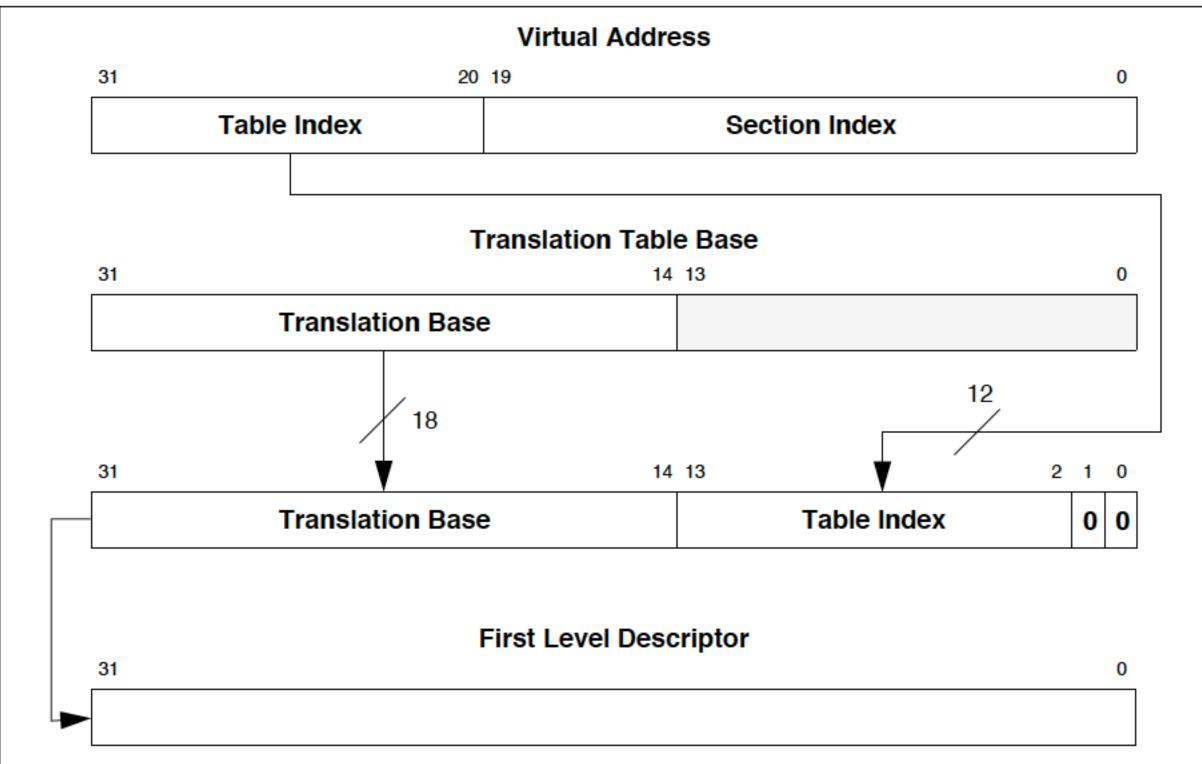

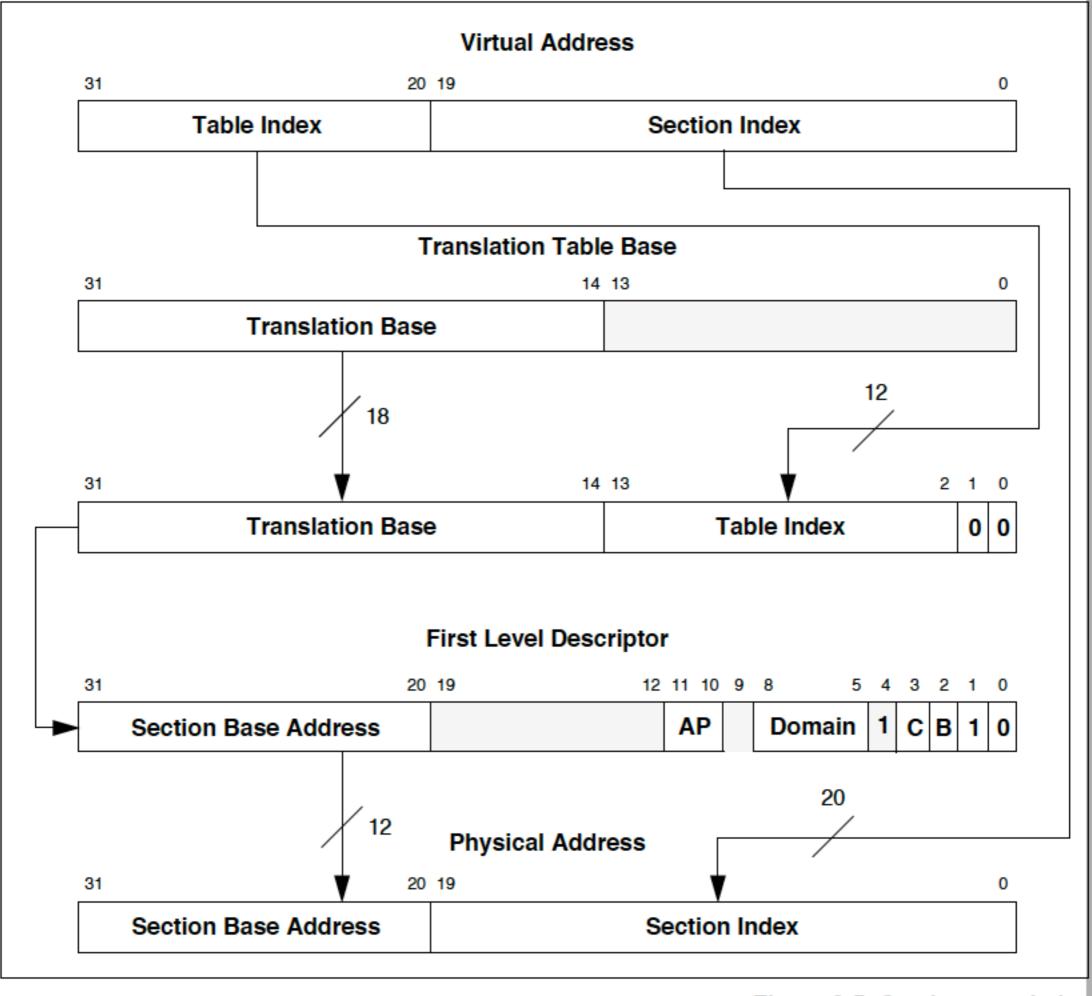

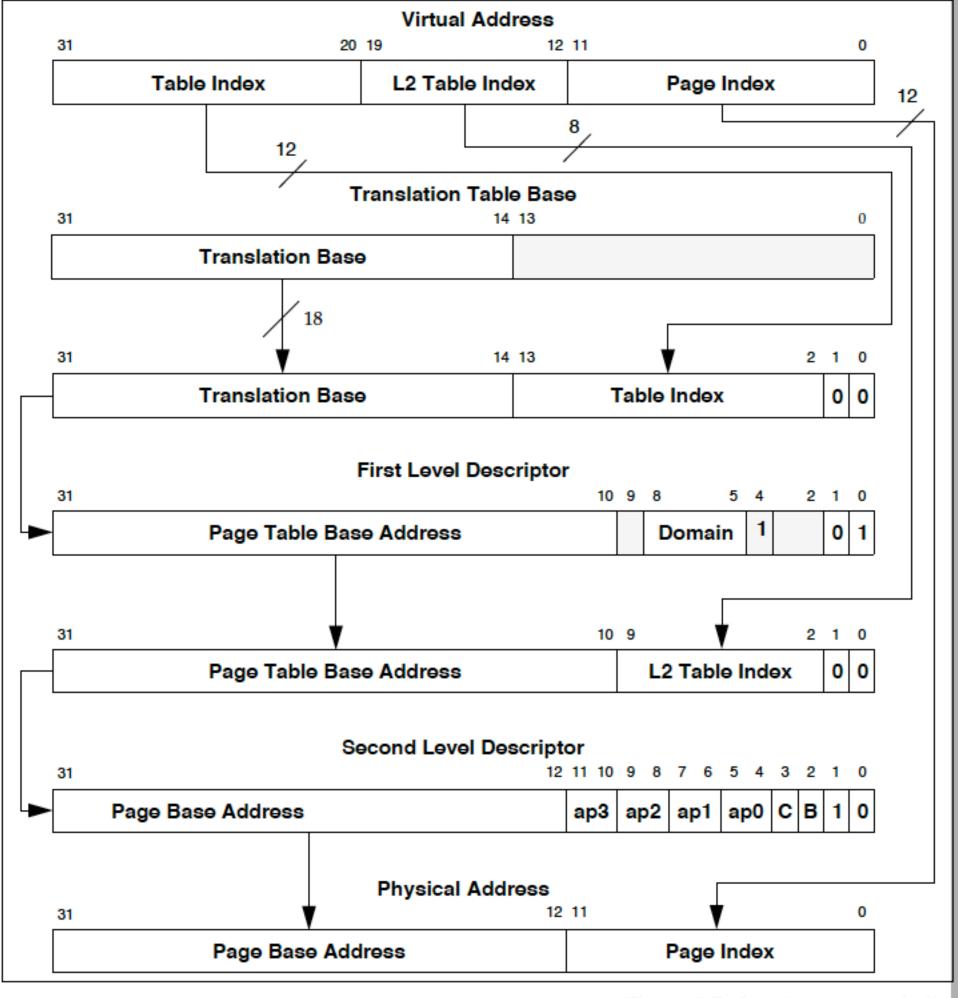

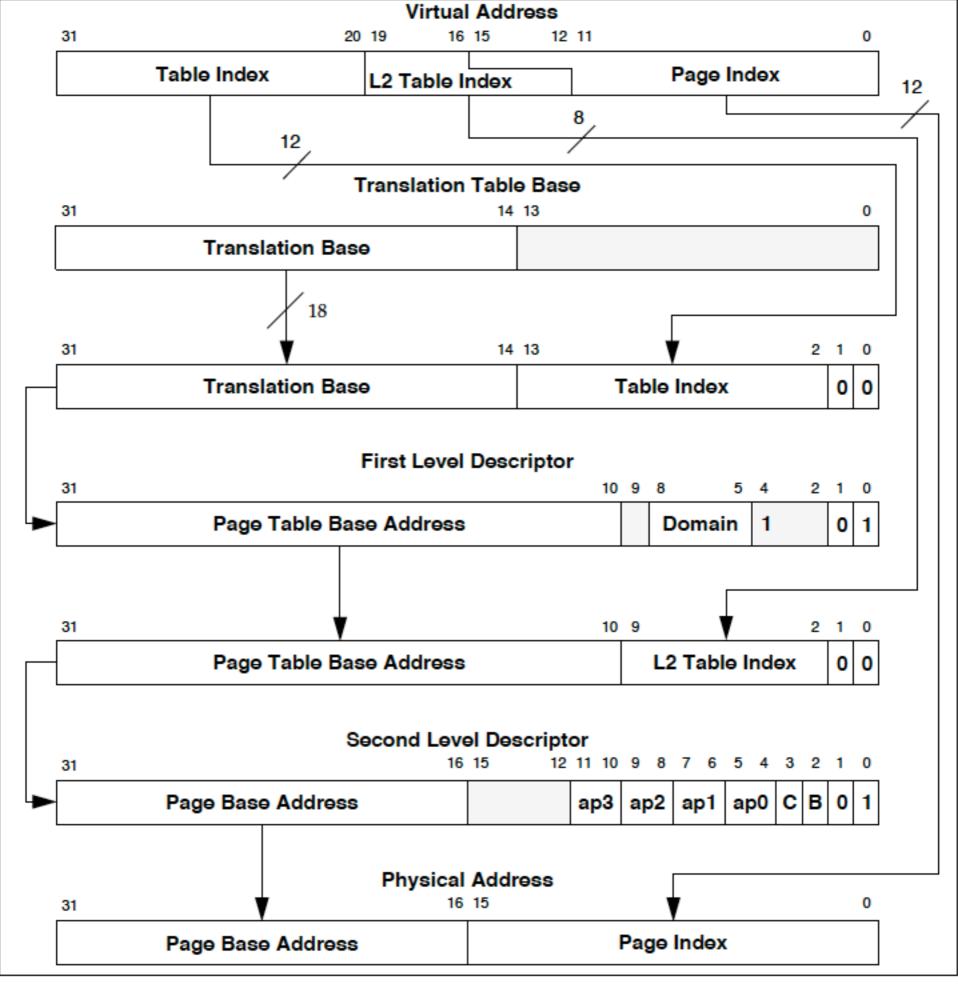

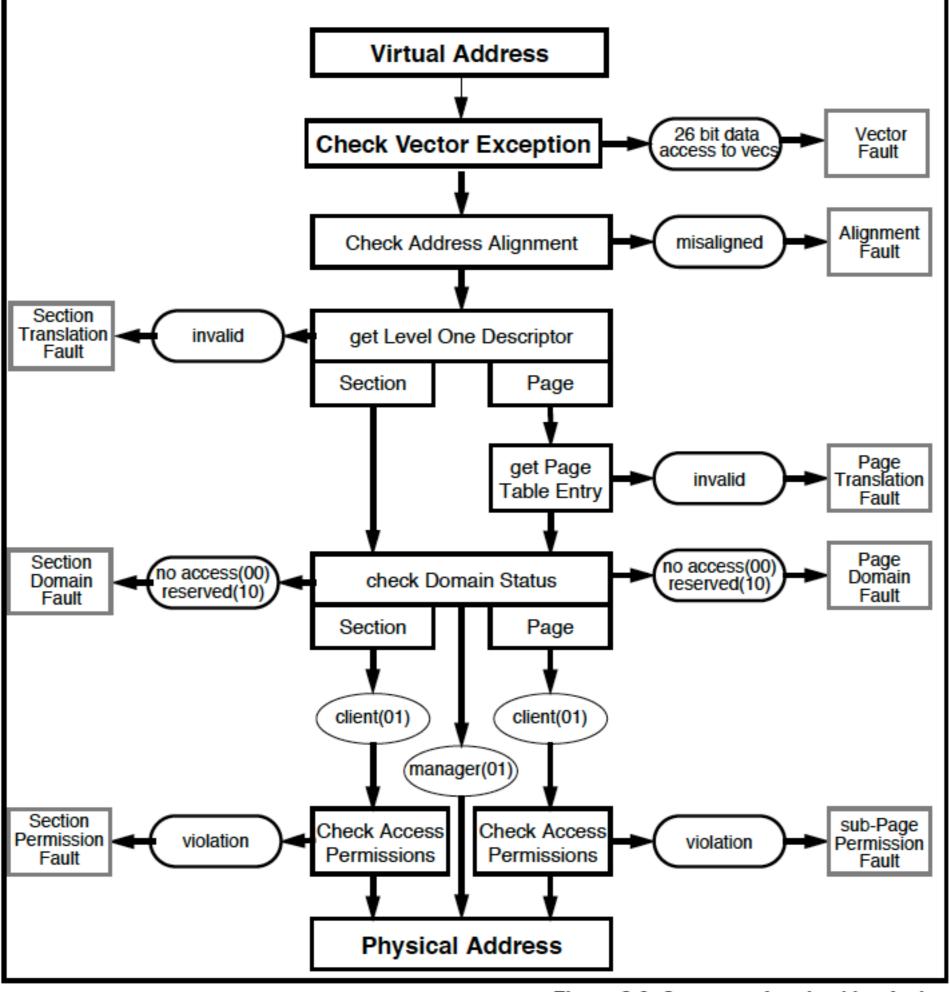

| Тема 7. Устройство за управление на паметта: Функции. Регистри. Транслация адресите. Дескриптори. Кеширане и буфериране. Грешки. Буфер за запис                                                                        | 1 час       |

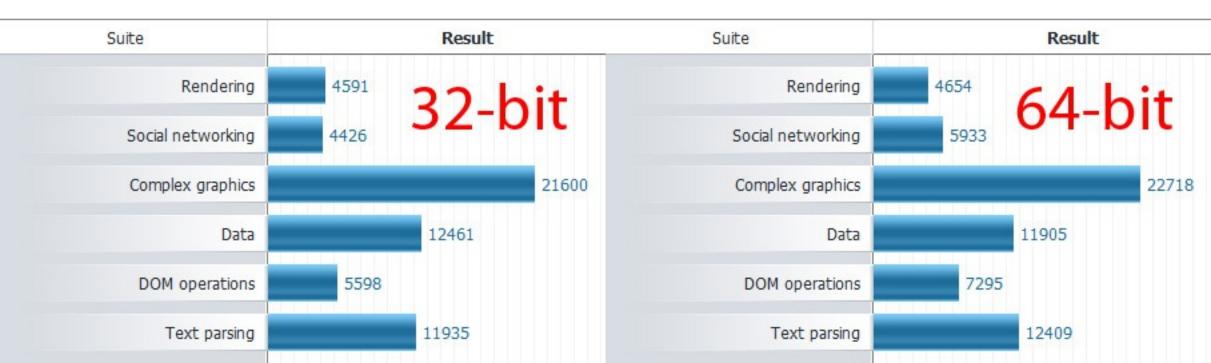

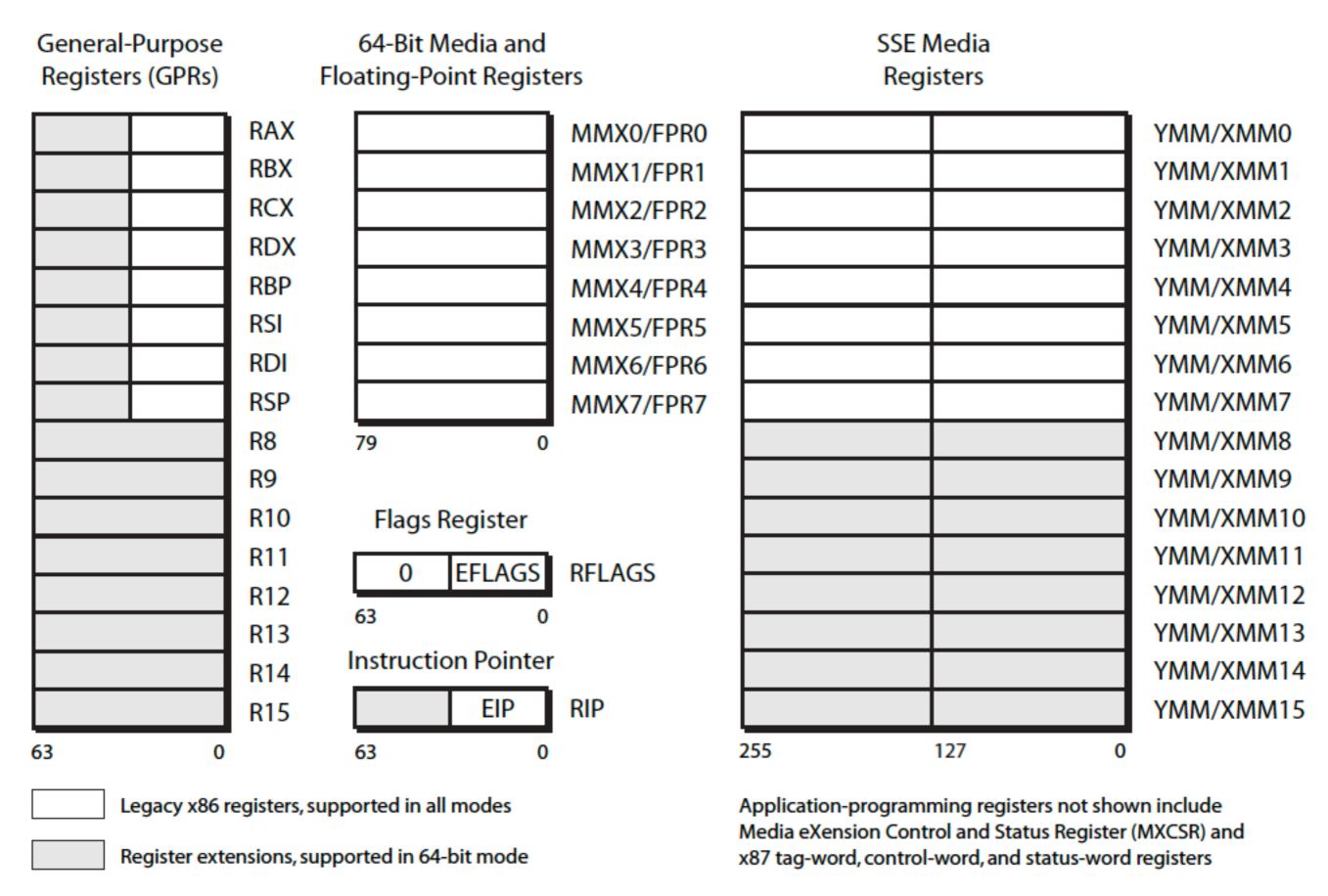

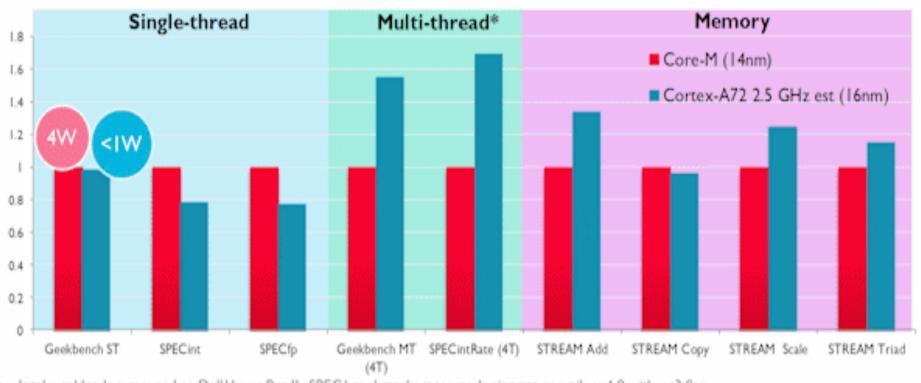

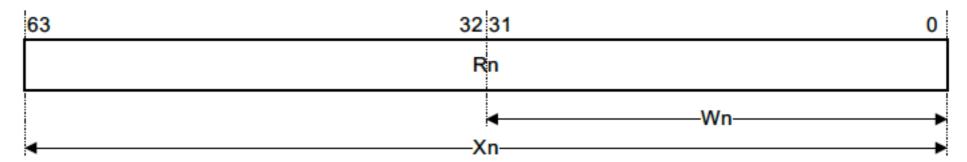

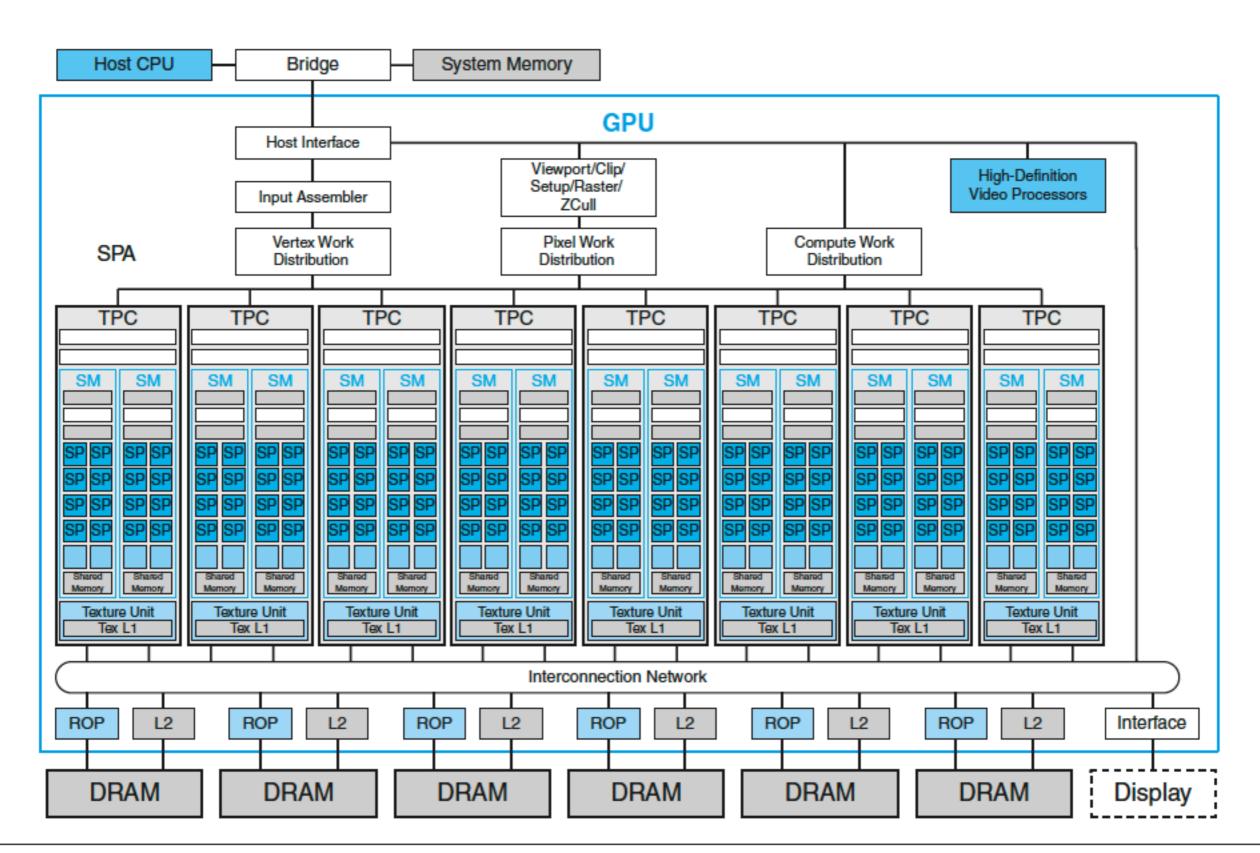

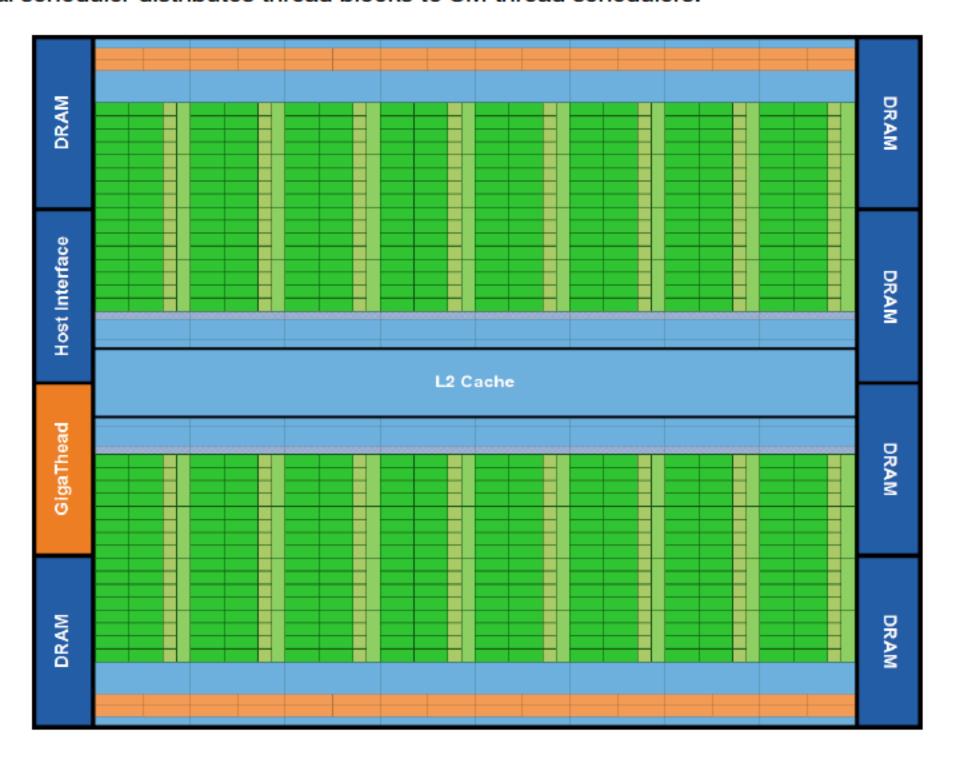

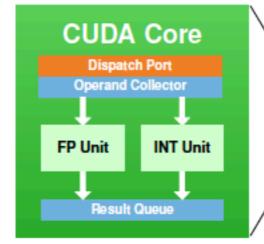

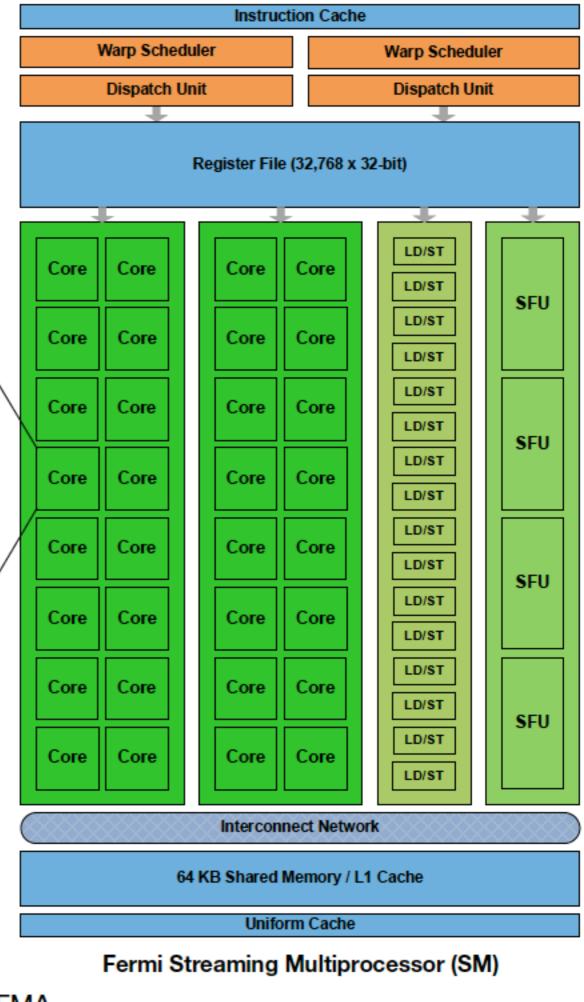

*Тема 8*. <u>Развитие на микропроцесорната архитектура:</u> Развитие на МП до 64-битова

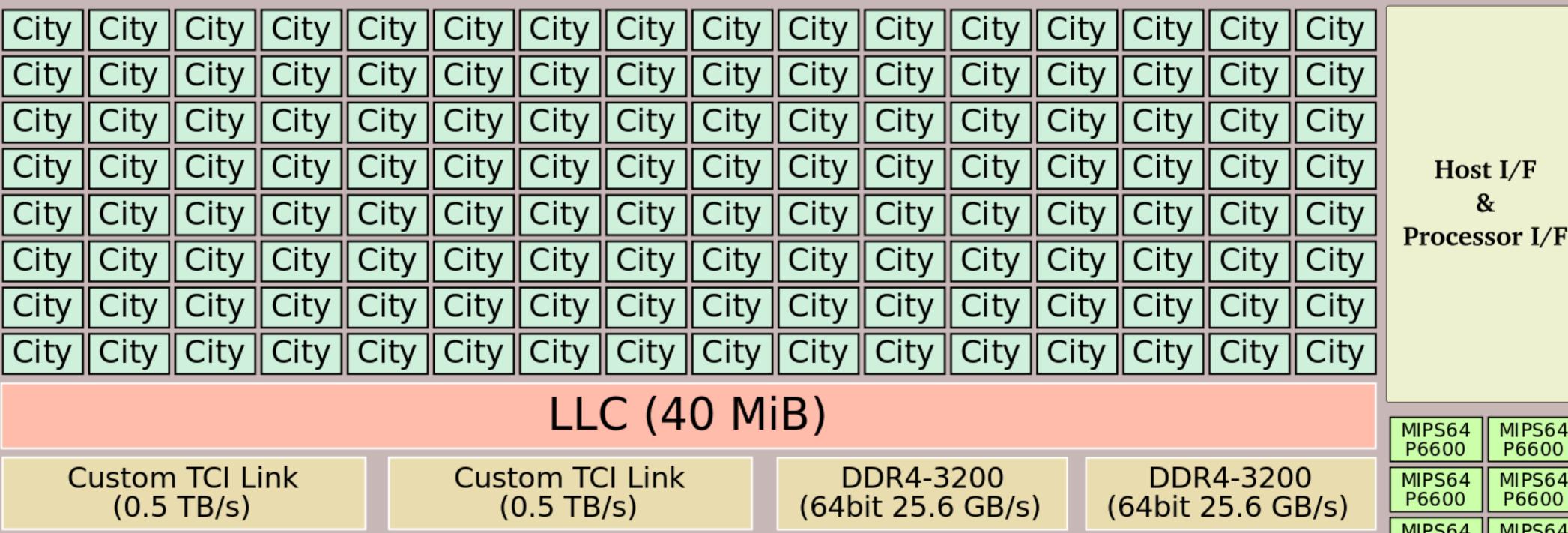

*Тема 9*. Кратки сведения за други МП: Условни преходи и пренос в МП без РКУ

("Alpha", MIPS). МП с "регистров прозорец" (SPARC). Програми "Здравей,

архитектура. Графични процесори. Многоядреност.

свят!" за различни МП и операционни системи (ОС).

2 часа

1 час

http://umis.tu-varna.bg/prep/upload/190/

| Year | recnnology used in computers         | Relative performance/ unit cost |

|------|--------------------------------------|---------------------------------|

| 1951 | Vacuum tube                          | 1                               |

| 1965 | Transistor                           | 35                              |

| 1975 | Integrated circuit                   | 900                             |

| 1995 | Very large-scale integrated circuit  | 2,400,000                       |

| 2013 | Ultra large-scale integrated circuit | 250,000,000,000                 |

# FIGURE 1.10 Relative performance per unit cost of technologies used in computers over time. Source: Computer Museum, Boston, with 2013 extrapolated by the authors. See Section 1.12.

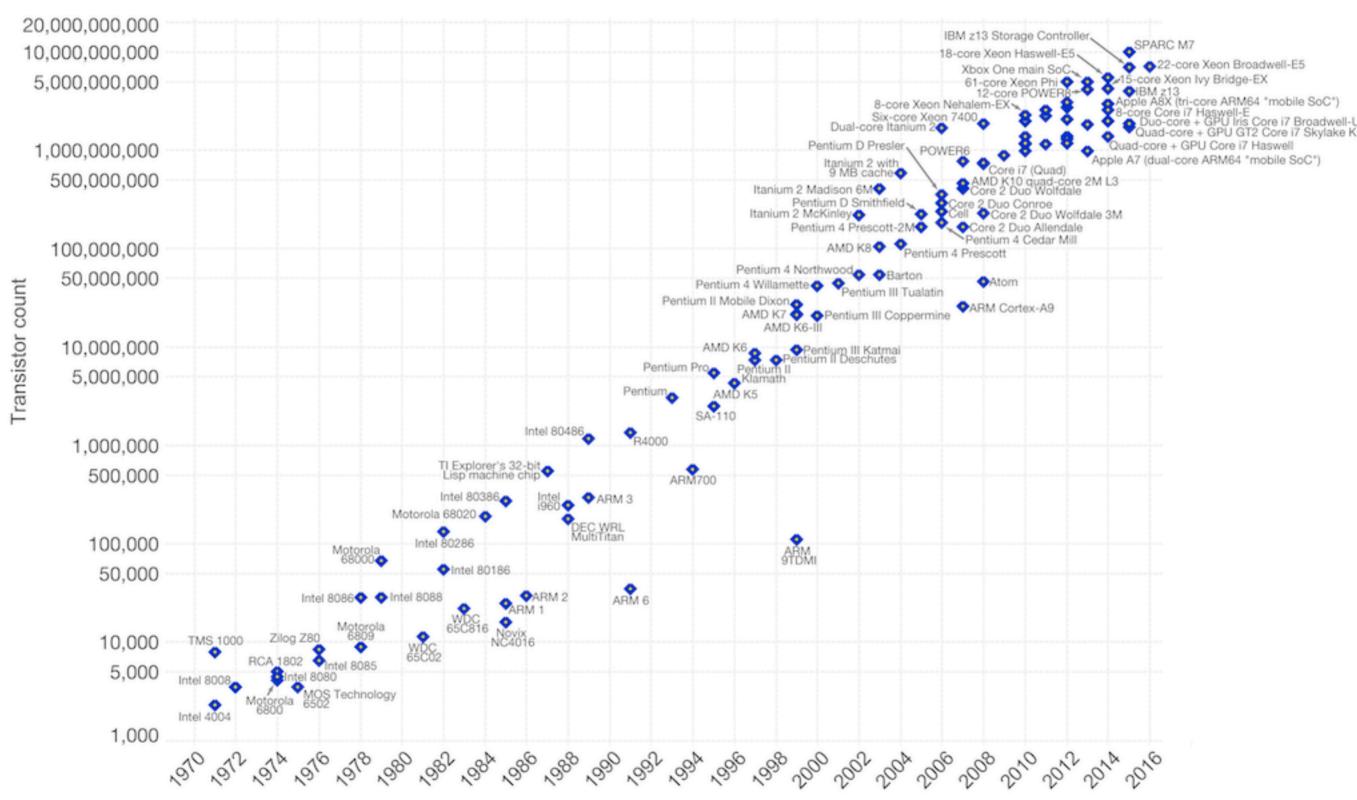

## Moore's Law – The number of transistors on integrated circuit chips (1971-2016)

Our World in Data

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years.

This advancement is important as other aspects of technological progress – such as processing speed or the price of electronic products – are strongly linked to Moore's law.

Original data collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond and C. Batten Dotted line extrapolations by C. Moore

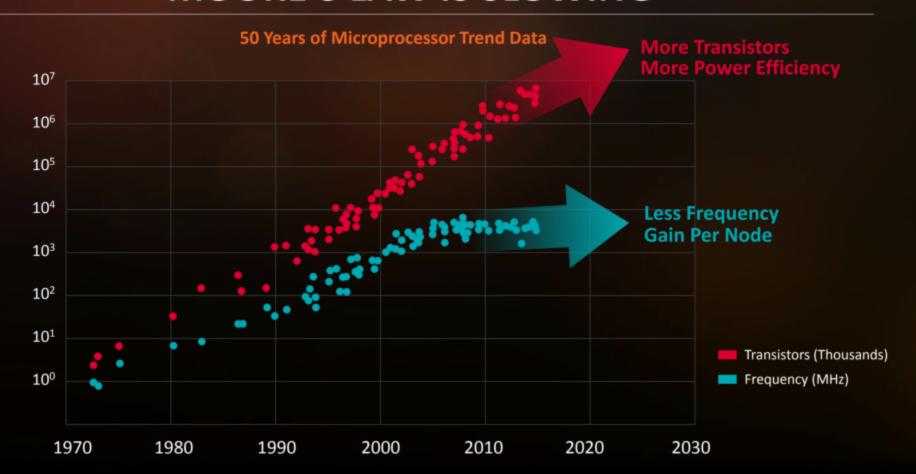

#### **MOORE'S LAW IS SLOWING**

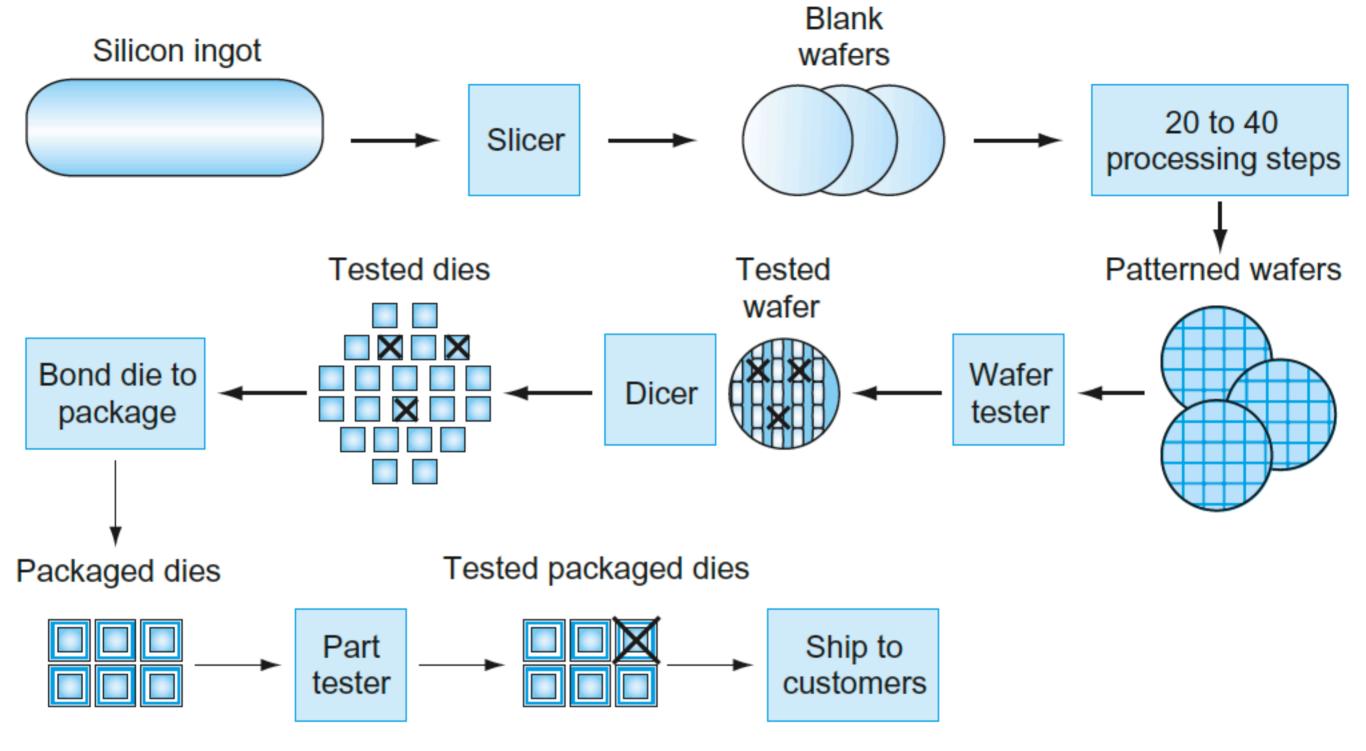

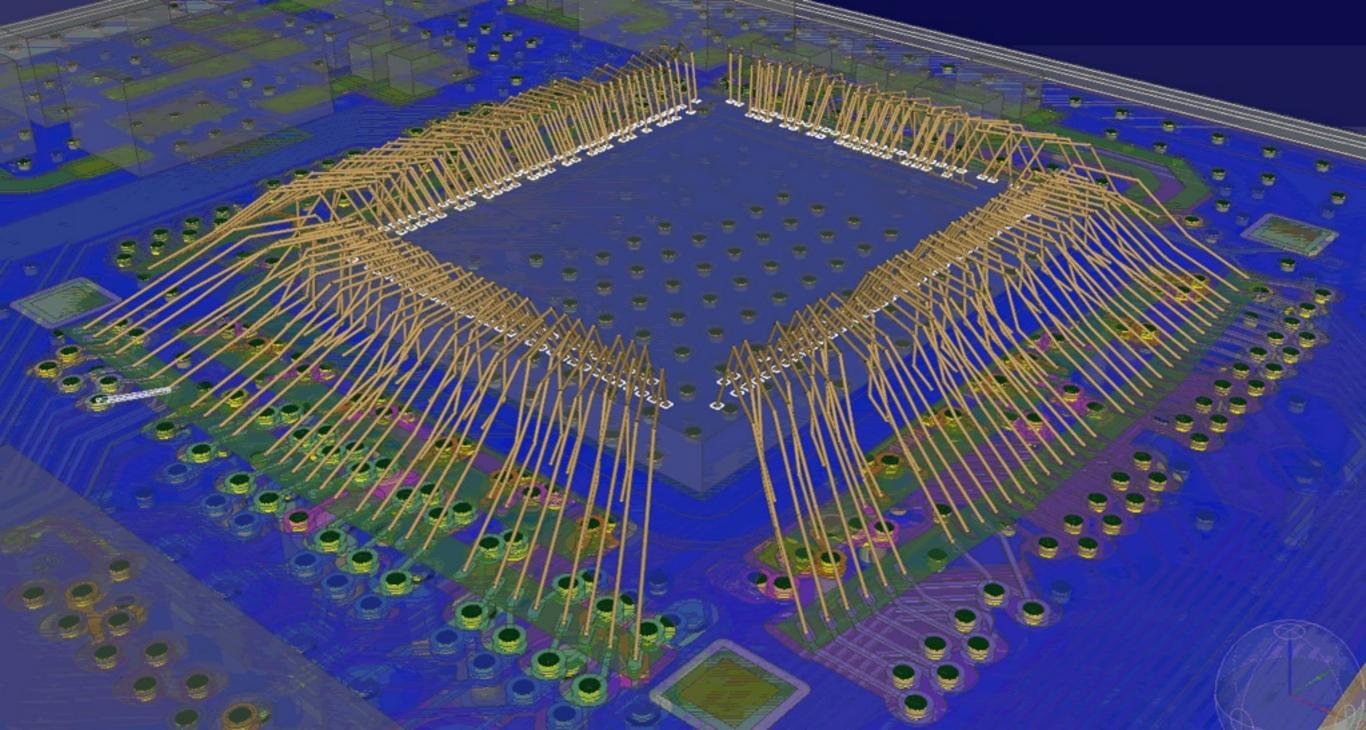

**FIGURE 1.12 The chip manufacturing process.** After being sliced from the silicon ingot, blank wafers are put through 20 to 40 steps to create patterned wafers (see Figure 1.13). These patterned wafers are then tested with a wafer tester, and a map of the good parts is made. Next, the wafers are diced into dies (see Figure 1.9). In this figure, one wafer produced 20 dies, of which 17 passed testing. (X means the die is bad.) The yield of good dies in this case was 17/20, or 85%. These good dies are then bonded into packages and tested one more time before shipping the packaged parts to customers. One bad packaged part was found in this final test.

### осношные электрические параметры в диапазоно температур от минус 60 °C до 85 °C

| Наямзнование параметра, единица измерения                  | Букренное   | Норма    |          |

|------------------------------------------------------------|-------------|----------|----------|

| T 13                                                       | обозначение | но меное | не более |

| I. Рамодное напрящение високого уровия, В ( Iow = -0.4 мA) | UON         | 2,4      |          |

| 2. Беленное напряжение инэкого урения, В ( Гос = 2,0 м/к)  | UoL.        |          | 0,45     |

| 3. Tok norpedments, MA                                     | Icc         |          | 360      |

| 4. Ток утечки на пходах, мкА                               | Ins         | 1        | ±10      |

| 5. Виходной ток в состоянии "Вислечено", мкА               | 102         | H        | ±10      |

| С. Входиал еслость, пФ                                     | CI          | +        |          |

| 7. Еммость ахода/вихода, ит                                |             |          | I5       |

|                                                            | C2/0        |          |          |

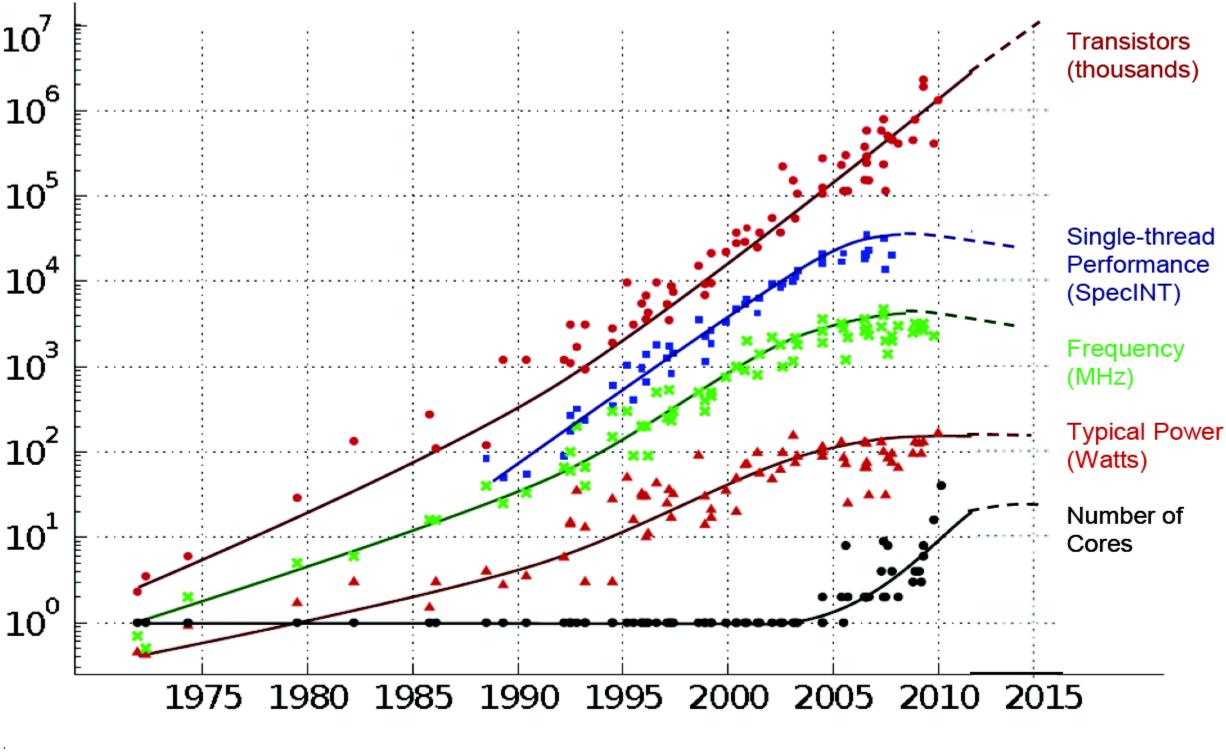

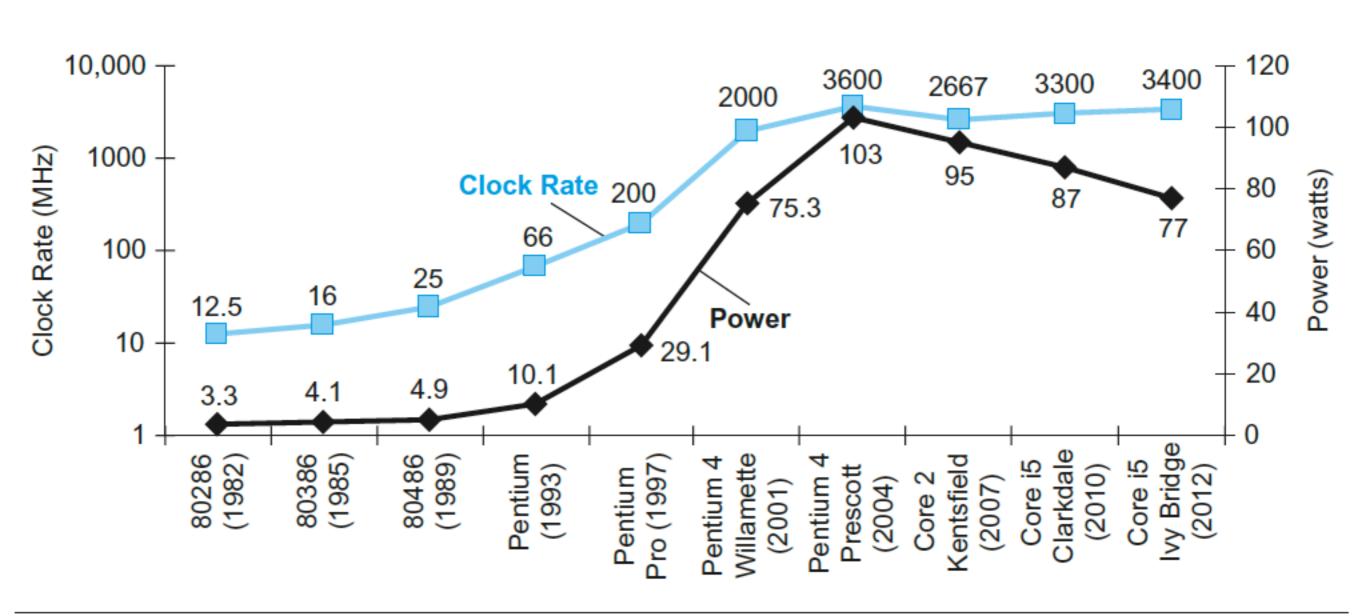

Figure 1.16 shows the increase in clock rate and power of eight generations of Intel microprocessors over 30 years. Both clock rate and power increased rapidly for decades and then flattened off recently. The reason they grew together is that they are correlated, and the reason for their recent slowing is that we have run into the practical power limit for cooling commodity microprocessors.

**FIGURE 1.16** Clock rate and Power for Intel x86 microprocessors over eight generations and 30 years. The Pentium 4 made a dramatic jump in clock rate and power but less so in performance. The Prescott thermal problems led to the abandonment of the Pentium 4 line. The Core 2 line reverts to a simpler pipeline with lower clock rates and multiple processors per chip. The Core i5 pipelines follow in its footsteps.

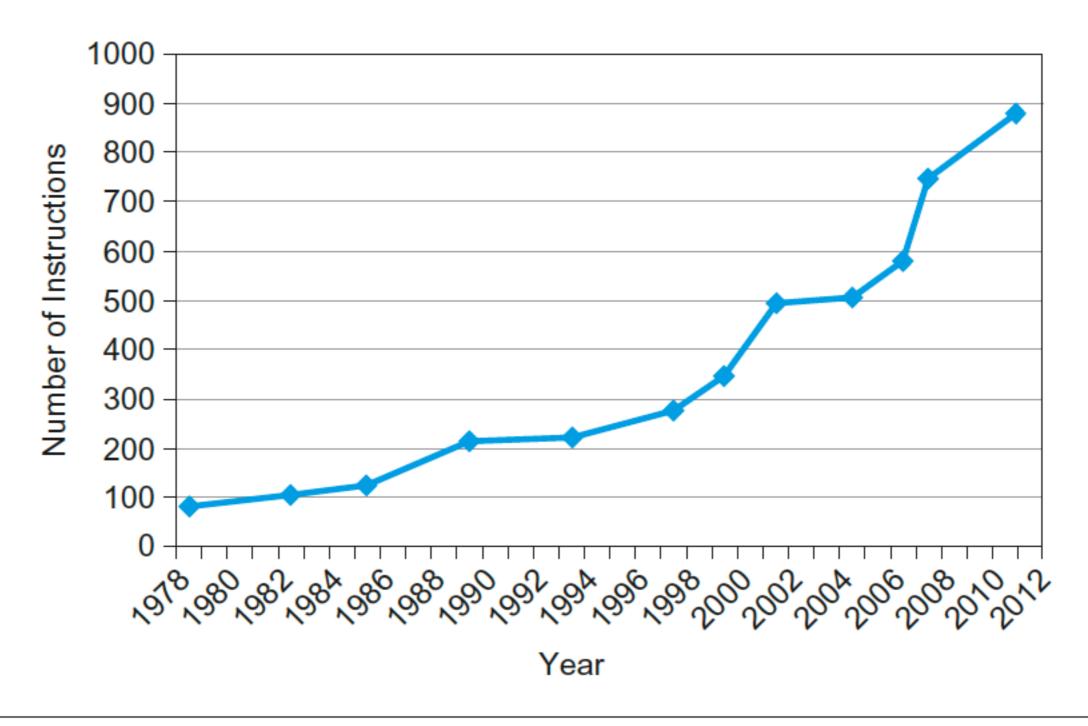

While backwards binary compatibility is sacrosanct, Figure 2.44 shows that the x86 architecture has grown dramatically. The average is more than one instruction per month over its 35-year lifetime!

**FIGURE 2.44 Growth of x86 instruction set over time.** While there is clear technical value to some of these extensions, this rapid change also increases the difficulty for other companies to try to build compatible processors.

| Прехвърляне                      | Аритметични                                | Побитови                      | За преходи                                                                                                                                | За низове                           | ПСУ                                          |

|----------------------------------|--------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|

| MOV, PUSH,<br>POP, XCHG,<br>XLAT | ADD, ADC,<br>AAA, DAA, INC                 | AND, OR,<br>XOR, NOT,<br>TEST | CALL, RET, JMP                                                                                                                            | REP, REPE/<br>REPZ, REPNE/<br>REPNZ | INT, INTO, IRET                              |

| IN, OUT                          | SUB, SBB,<br>AAS, DAS,<br>DEC, NEG,<br>CMP | SAL/SHL,<br>SAR, SHR          | JA/JNBE, JAE/ JNB/JNC, JB/ JNAE/JC, JBE/ JNA, JCXZ, JE/JZ, JG/JNLE, JGE/JNL, JL/JNGE, JLE/JNG, JNE/JNZ, JNO, JNP/JPO, JNS, JO, JP/JPE, JS | MOVSB,<br>MOVSW                     | STC, CLC,<br>CMC, STD,<br>CLD, STI, CLI      |

| LEA, LDS, LES                    | MUL, IMUL,<br>AAM                          | ROL, ROR,<br>RCL, RCR         | LOOP, LOOPE/<br>LOOPZ, LOOPNE/<br>LOOPNZ                                                                                                  | CMPSB,<br>CMPSW                     | HLT, WAIT,<br>LOCK (ESC е за<br>копроцесор!) |

| LAHF, SAHF,<br>PUSHF, POPF       | DIV, IDIV, AAD                             |                               |                                                                                                                                           | SCASB, SCASW                        | (NOP – това е<br>XCHG AX,AX !)               |

|                                  | CBW, CWD                                   |                               |                                                                                                                                           | LODSB,<br>LODSW,<br>STOSB, STOSW    | +SALC (недо-<br>кументирана)<br>= 96 бр.     |

| 1978 | 96  | 8086 (3,2 μm nMOSFET)         |                                        |

|------|-----|-------------------------------|----------------------------------------|

| 1980 | 83  | 8087 (3 μm)                   |                                        |

| 1982 | 105 | 80186                         |                                        |

| 1982 | 112 | 80286                         |                                        |

| 1982 | 84  | 80287                         |                                        |

| 1985 | 166 | 80386 (1,5 μm CHMOS III)      |                                        |

| 1987 | 96  | 80387                         |                                        |

| 1989 | 267 | 80486DX/P4 (1 μm CHMOS IV)    | FPU                                    |

| 1993 | 273 | 80586/P5/Pentium(0,8μ BiCMOS) | FPU                                    |

| 1995 | 304 | 80686/P6/Pentium Pro (350 nm) | FPU                                    |

| 1997 | 321 | Pentium MMX (280 nm)          | FPU, MMX                               |

| 1997 | 333 | 6x86MX (Cyrix)                | FPU, MMX, EMMI                         |

| 1998 | 353 | K6-2 (AMD, 250 nm)            | FPU, MMX, 3DNow!                       |

| 1999 | 358 | K6-2+ (AMD, 180 nm)           | FPU, MMX, Enhanced 3DNow!              |

| 1999 | 420 | Pentium III (250 nm CMOS)     | FPU, MMX, SSE                          |

| 2000 | 489 | Pentium 4 (180 nm)            | FPU, MMX, SSE, SSE2                    |

| 2003 | 528 | K8 / Athlon 64 (AMD, 130 nm)  | FPU,MMX,Enhanced 3DNow!,SSE,SSE2,AMD64 |

| 2004 | 499 | Pentium 4 Prescott (90 nm)    | FPU, MMX, SSE, SSE2, SSE3              |

#### Октомври 2015 г.: Xeon E3 v5 Skylake-DT (14 nm FinFET):

```

208 + 5 (CLMUL = Carry-less Multiplication) + 24 (BMI = Bit Manipulation Instructions)

```

- + 96 (FPU) + 20 (FMA = Fused Multiply-Add) =

- + 48 (MMX = Multimedia Extensions | Multiple Math Extensions | Matrix Math Extensions)

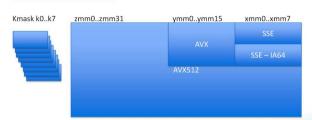

- + 68 (SSE = Streaming SIMD (Single Instruction, Multiple Data) Extensions)

- + 69 (SSE2)

- + 10 (SSE3)

- + 16 (SSSE3 = Supplemental SSE) = 515

- + 49 (SSE4.1)

- + 6 (SSE4.2)

- + 14 (x86-64)

- + 2 (ADX = Multi-Precision Add-Carry Instruction Extensions)

- + 12 (AVX = Advanced Vector Extensions)

- + 30 (AVX2)

- +13+6+8+8+8+18+2+44+12+16+63+6+10+16+12+9+2 (253 AVX3)

- + 8 (MPX = Memory Protection Extensions)

- + 4 (TSX = Transactional Synchronization Extensions) + 2 (SGX = Software Guard Extensions)

- + 10 (VT-x Virtualization) + 7 (AES-NI = Advanced Encryption Standard New Instructions) = 961

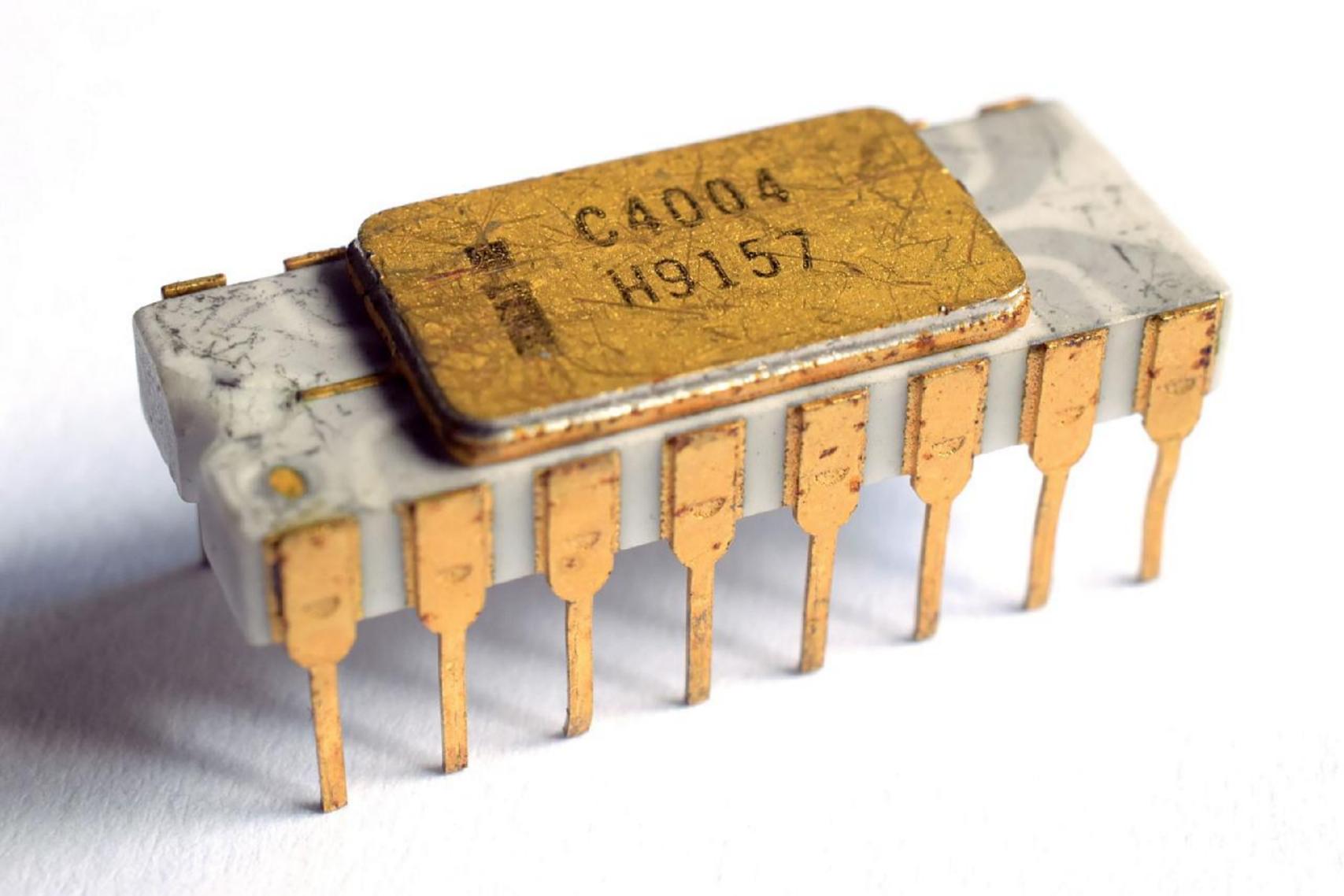

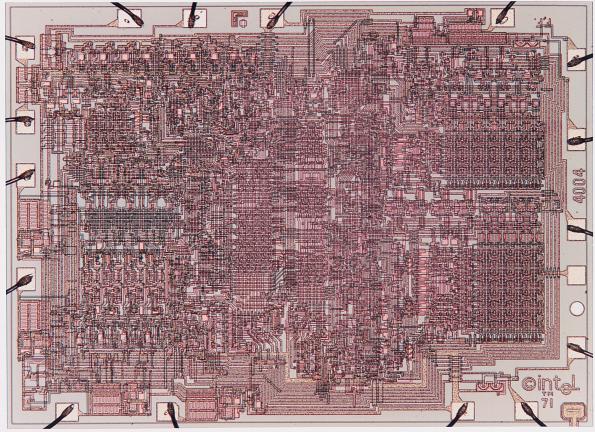

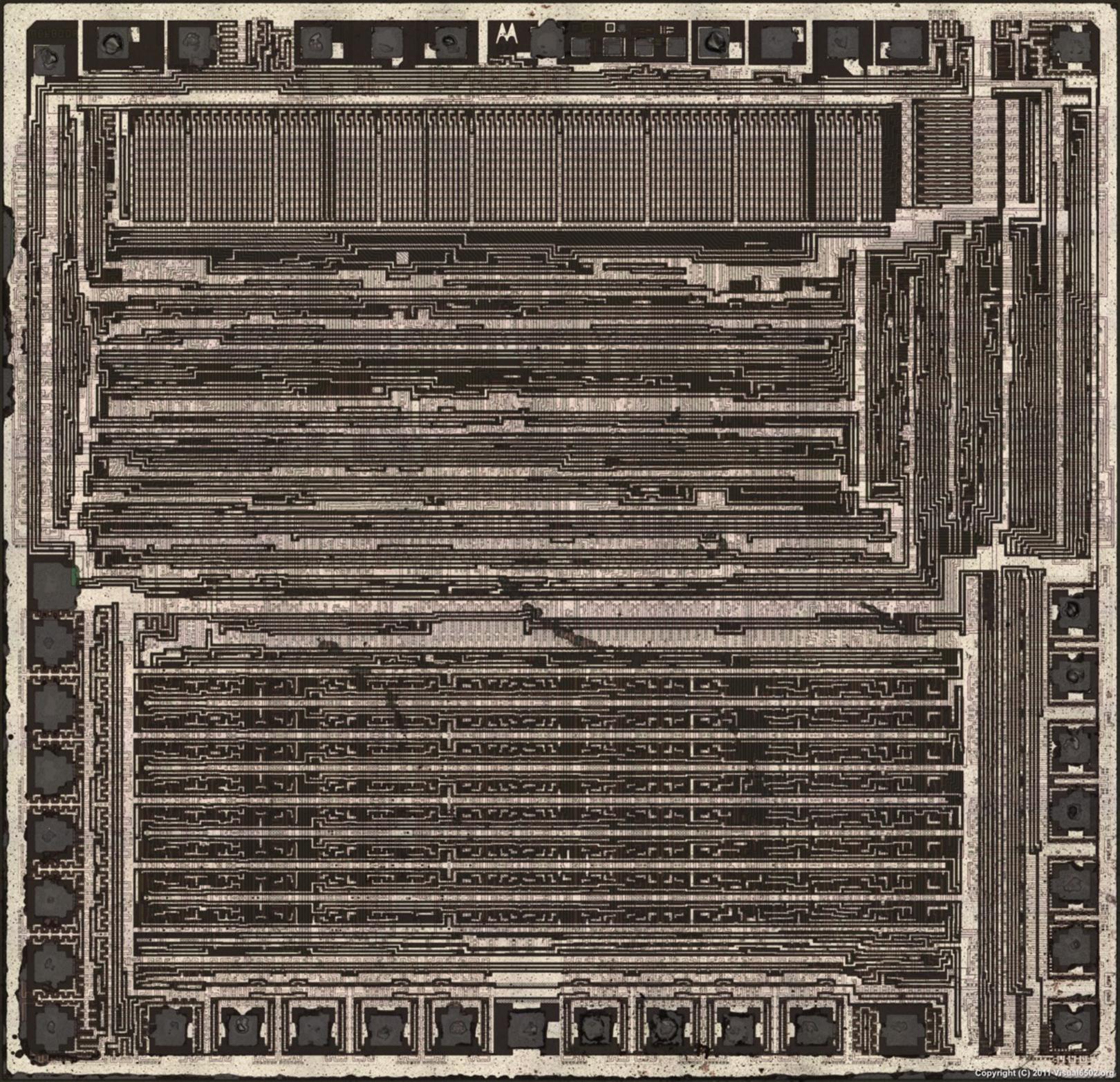

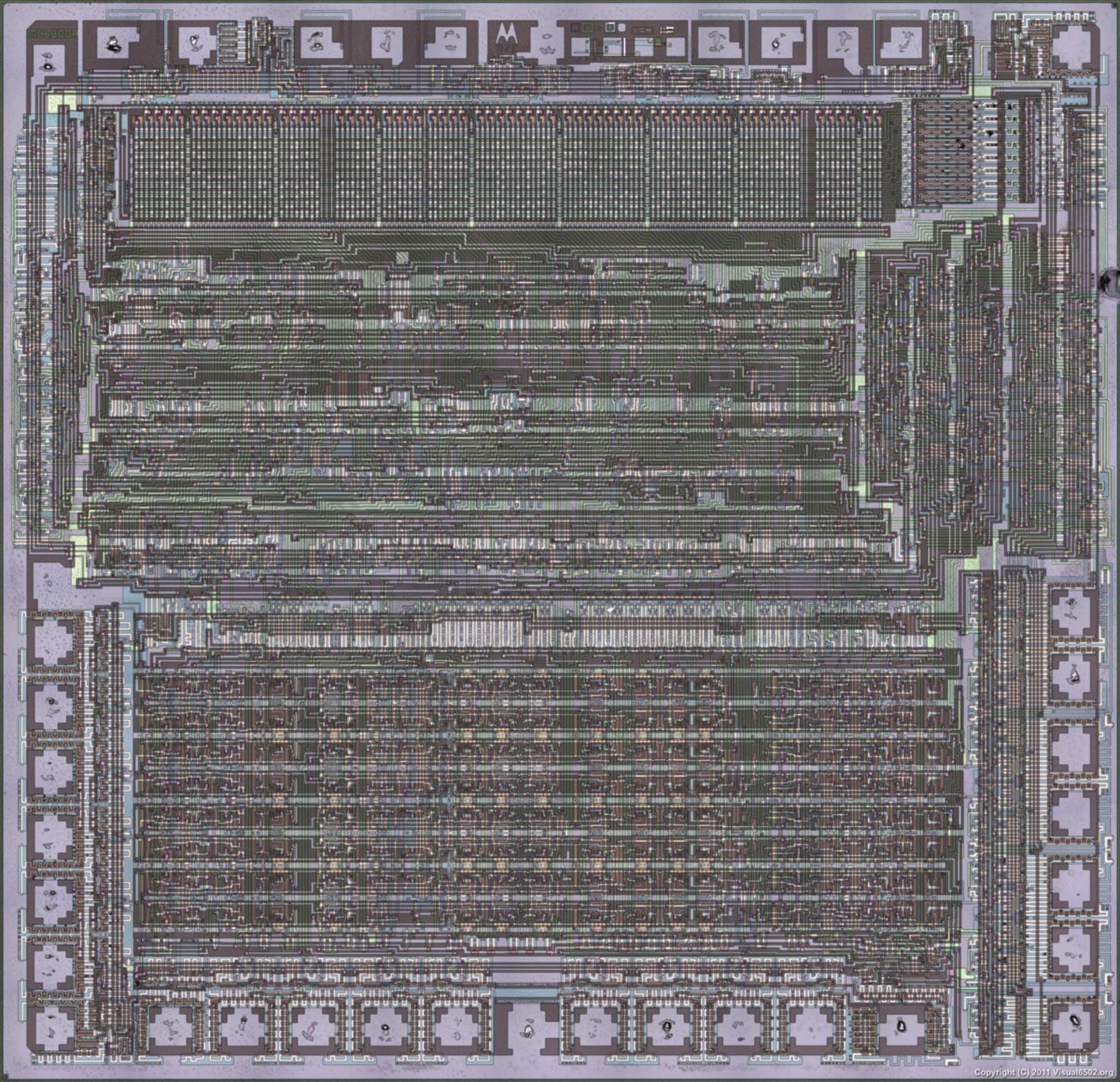

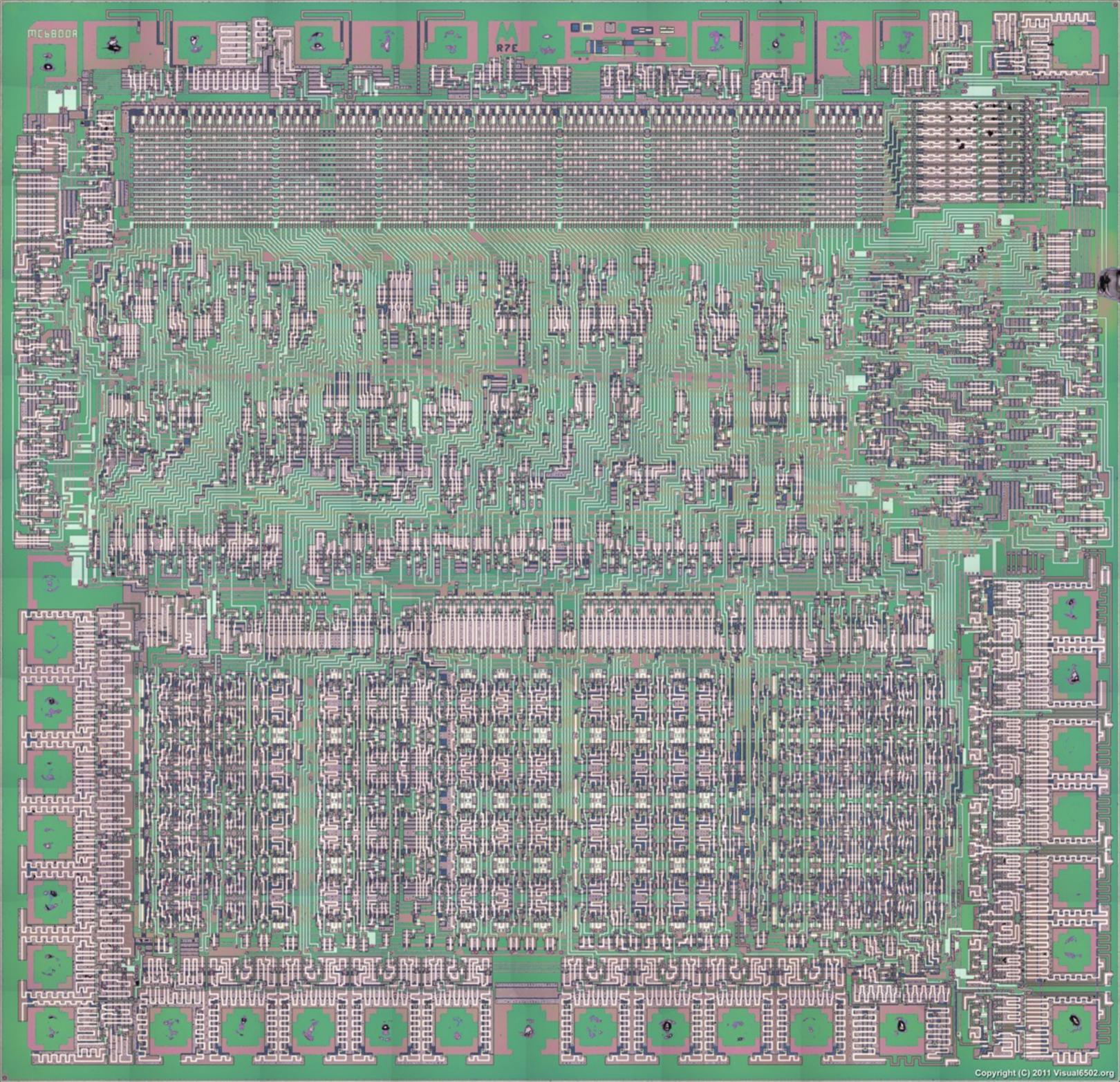

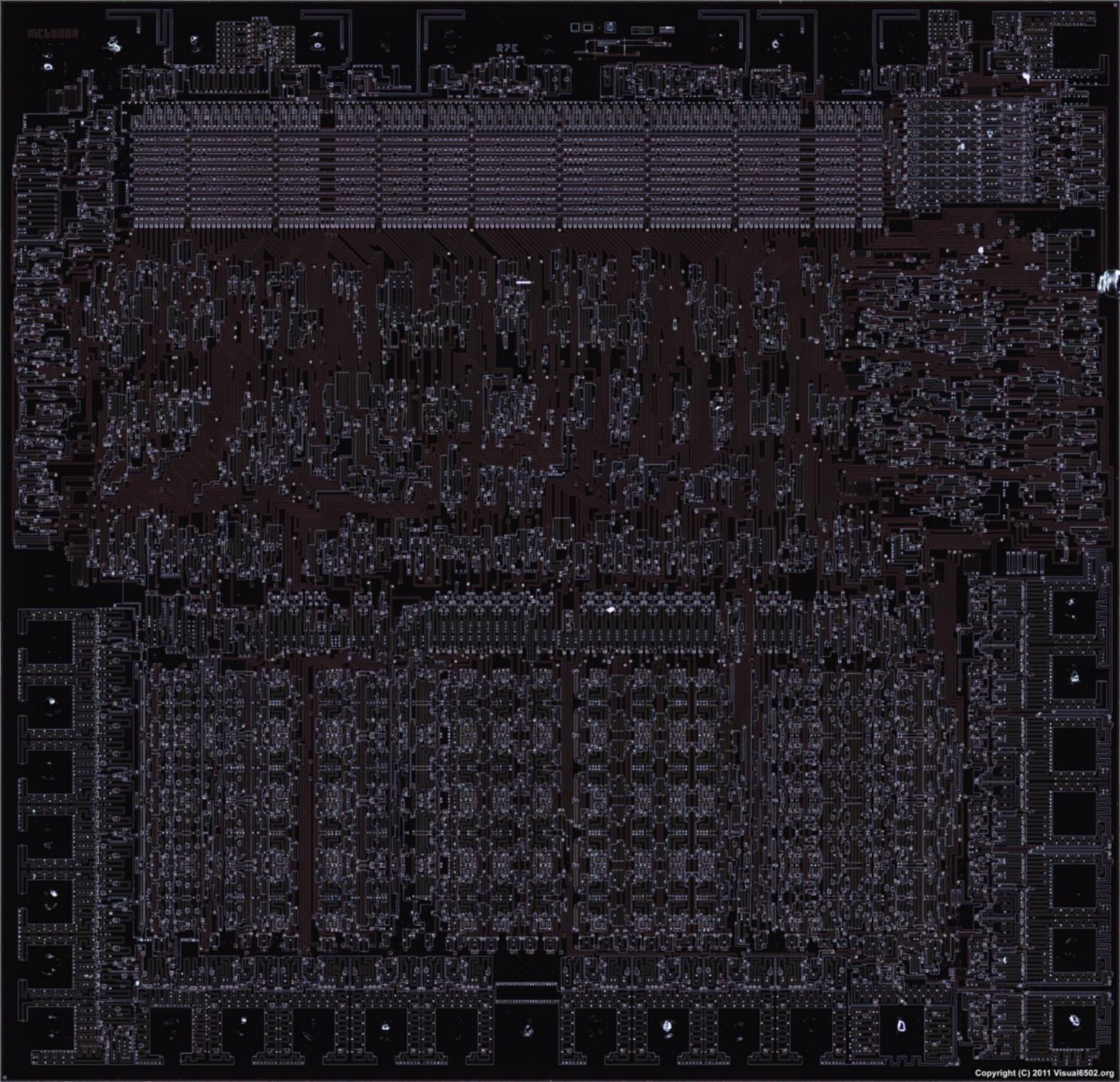

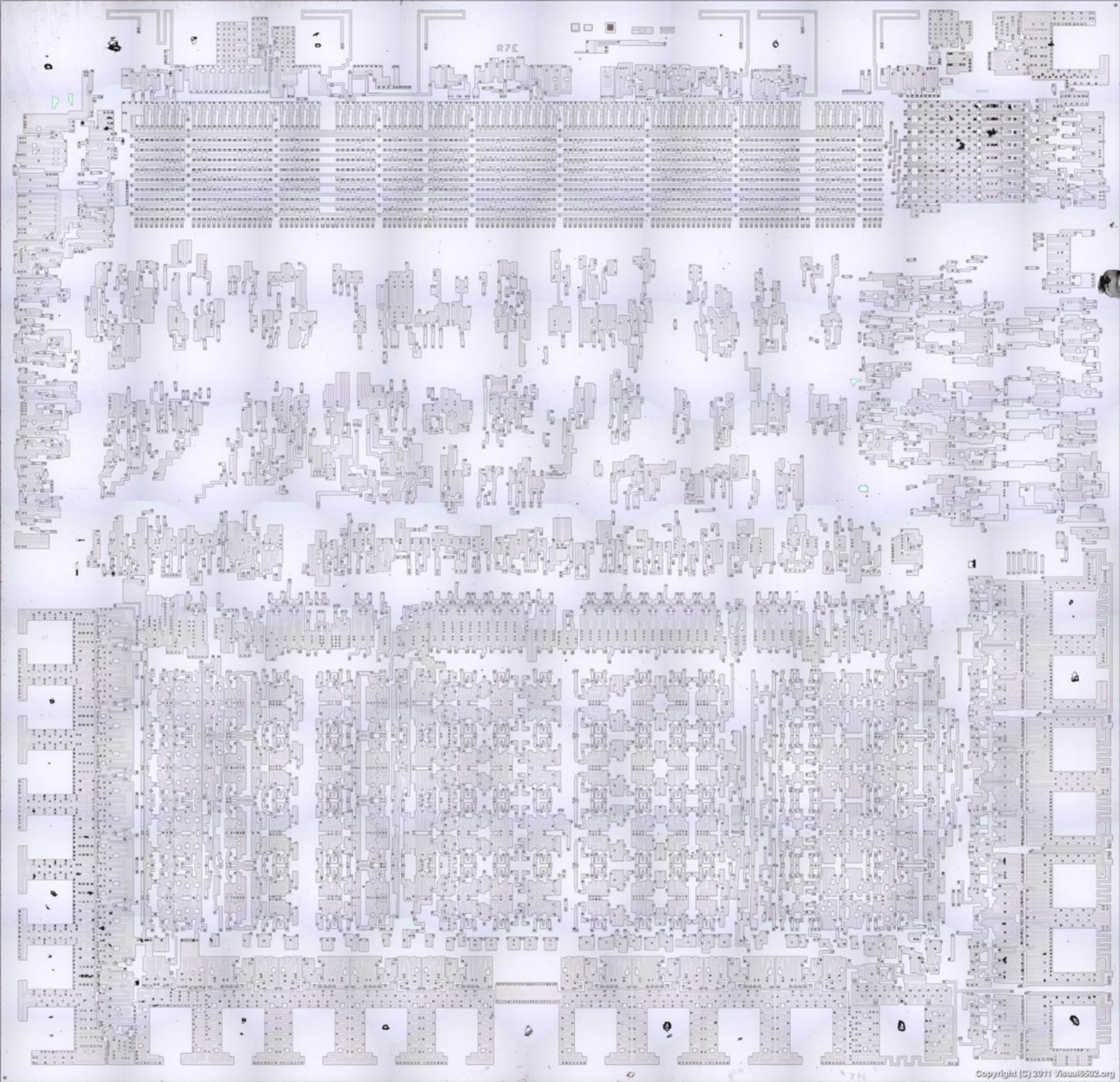

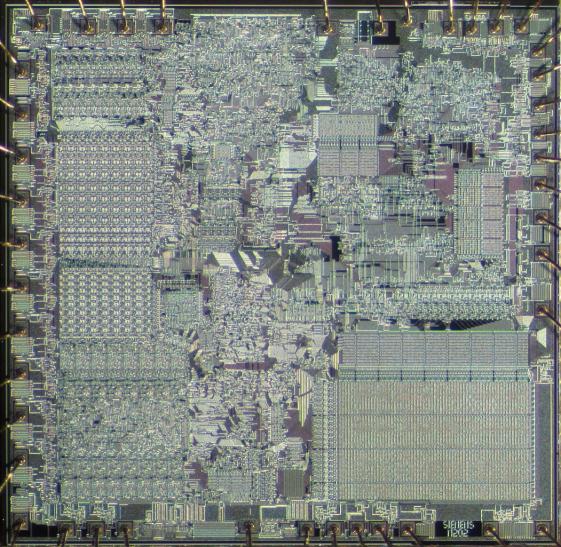

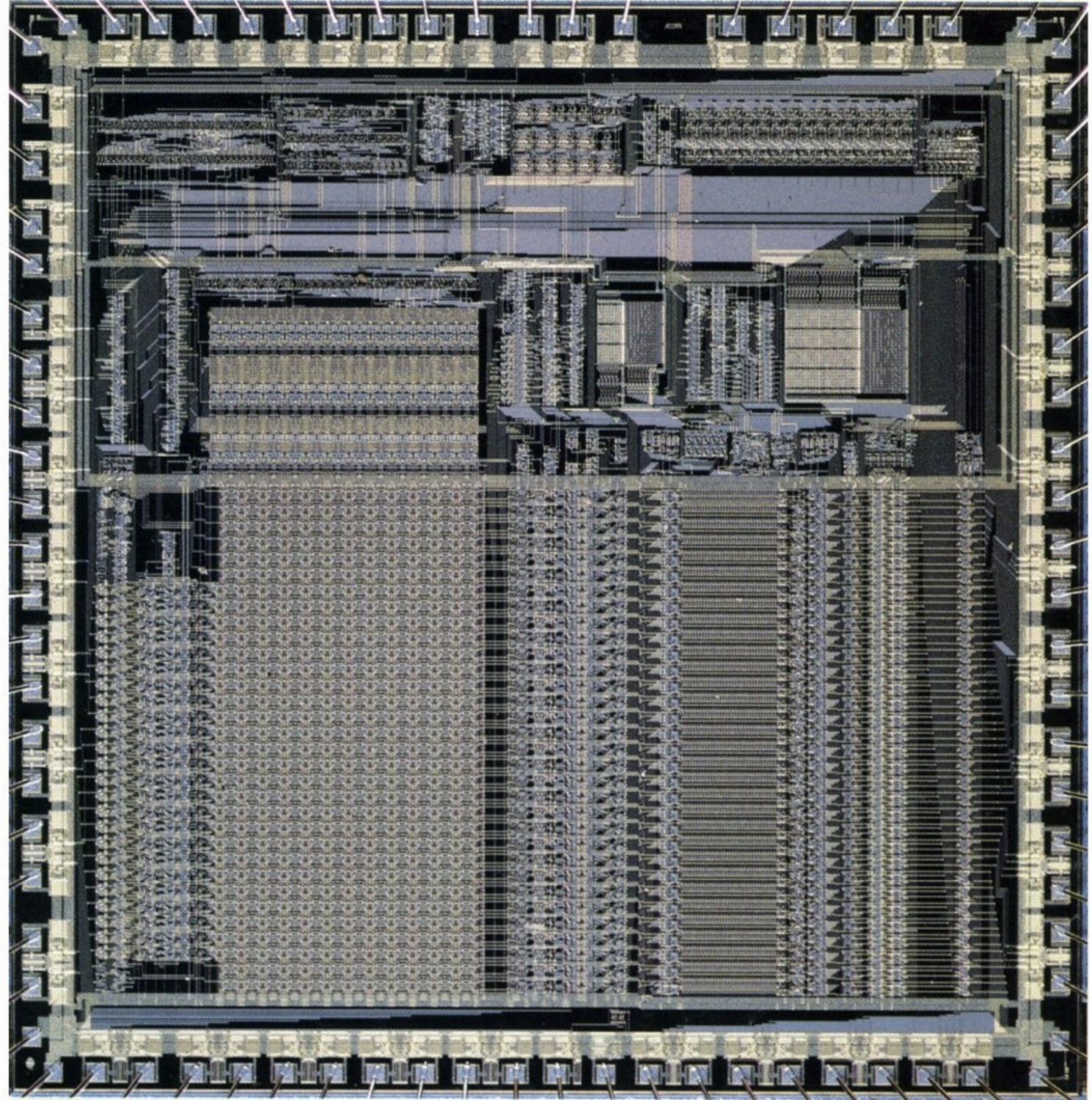

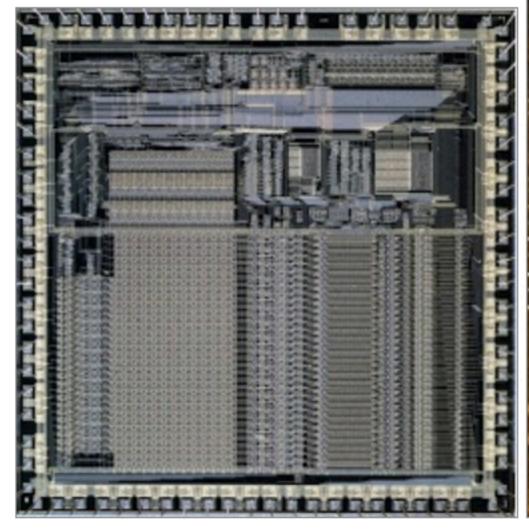

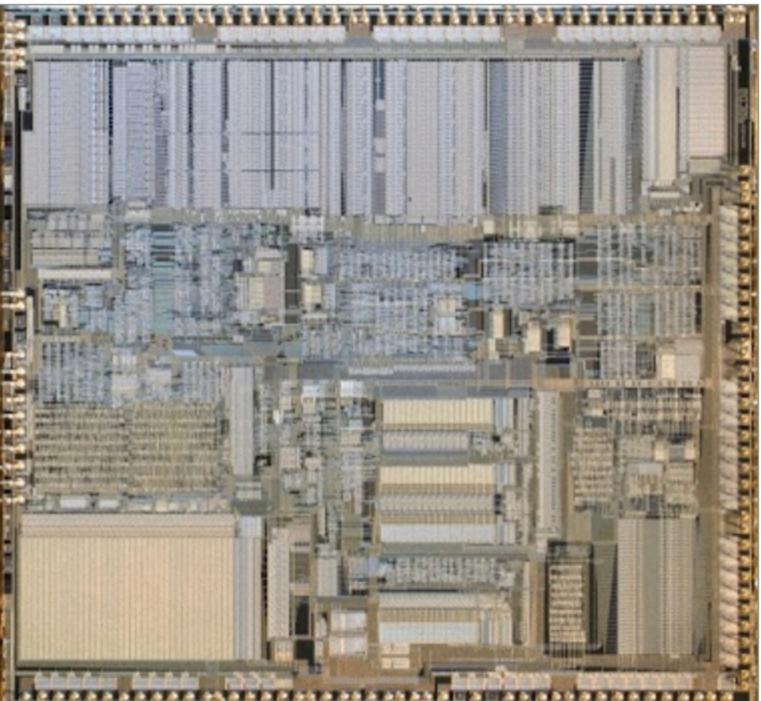

Die photos of the ARM1 processor and the Intel 386 processor to the same scale. The ARM1 is much smaller and contained 25,000 transistors compared to 275,000 in the 386. The 386 was higher density, with a 1.5 micron process compared to 3 micron for the ARM1. ARM1 photo courtesy of Computer History Museum. Intel A80386DX-20 by Pdesousa359, CC BY-SA 3.0.

Because of the ARM1's small transistor count, the chip used very little power: about 1/10 Watt, compared to nearly 2 Watts for the 386. The combination of high performance and low power

#### 2.1 Overview (4)

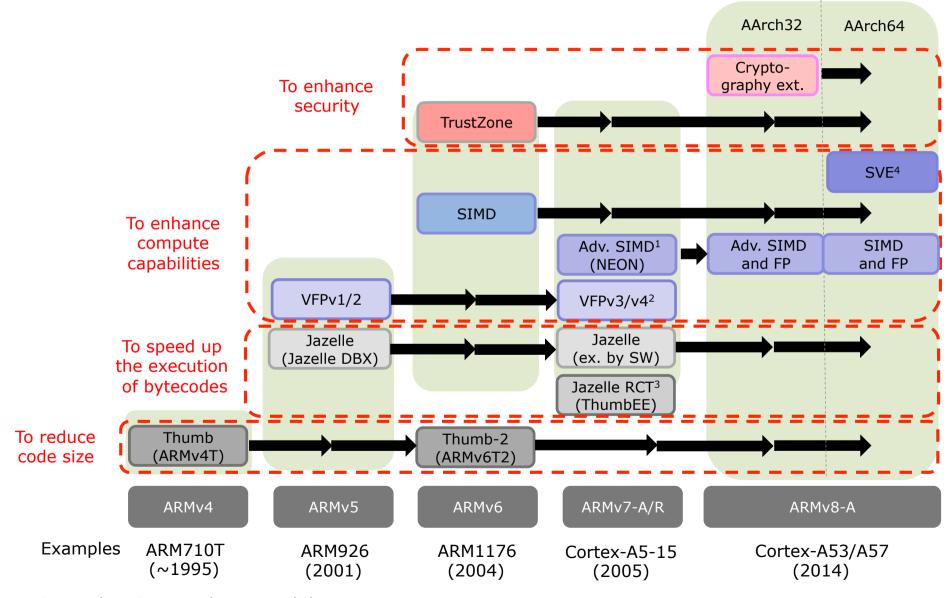

#### Main extensions introduced in ARM's basic ISA (simplified) -2 (Based on [64])

Remarks: See on the next slide.

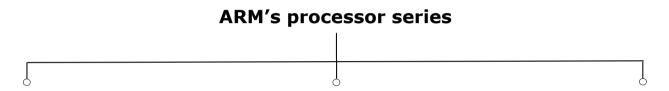

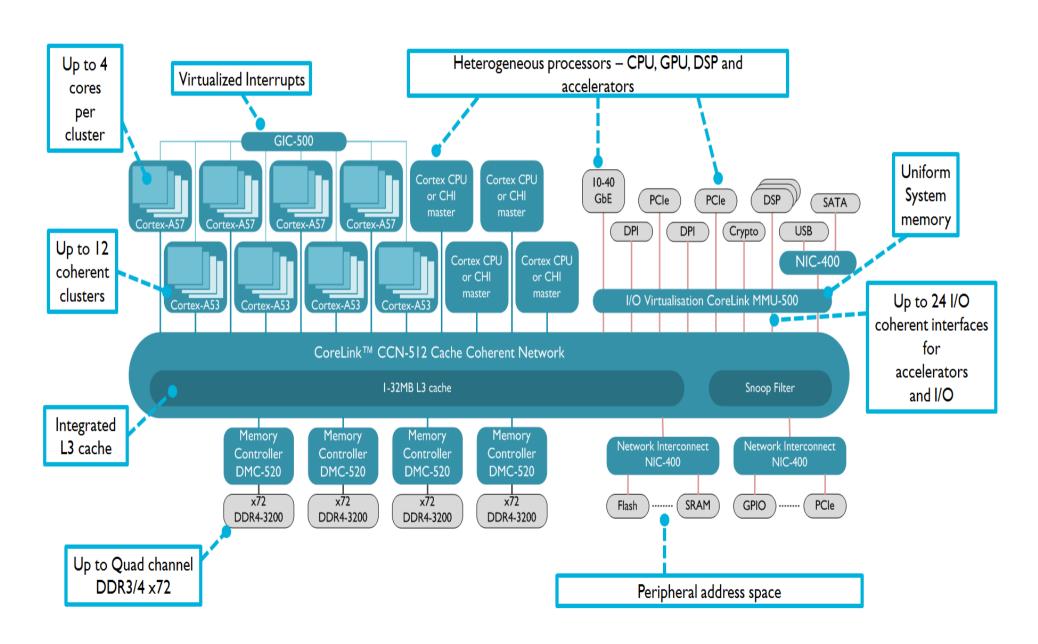

#### 3.1 Overview of ARM's processor lines (1)

#### 3.1 Overview of ARM's processor series

Subsequently, we give an overview of ARM's processor series subdivided into three sections, according their underlying ISAs, as follows.

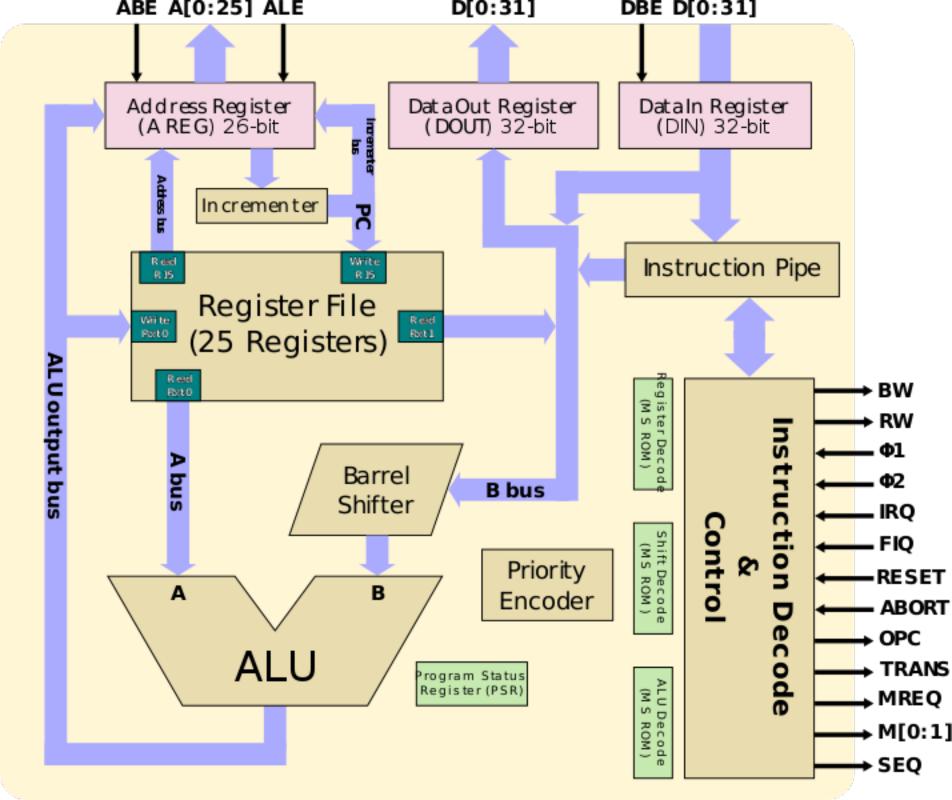

#### Processors implementing the ARMv1 – ARMv2 ISA

(Earliest ARM processors) (~ 1985-1990)

ARM1-ARM3

26-bit address bus 32-bit data buses

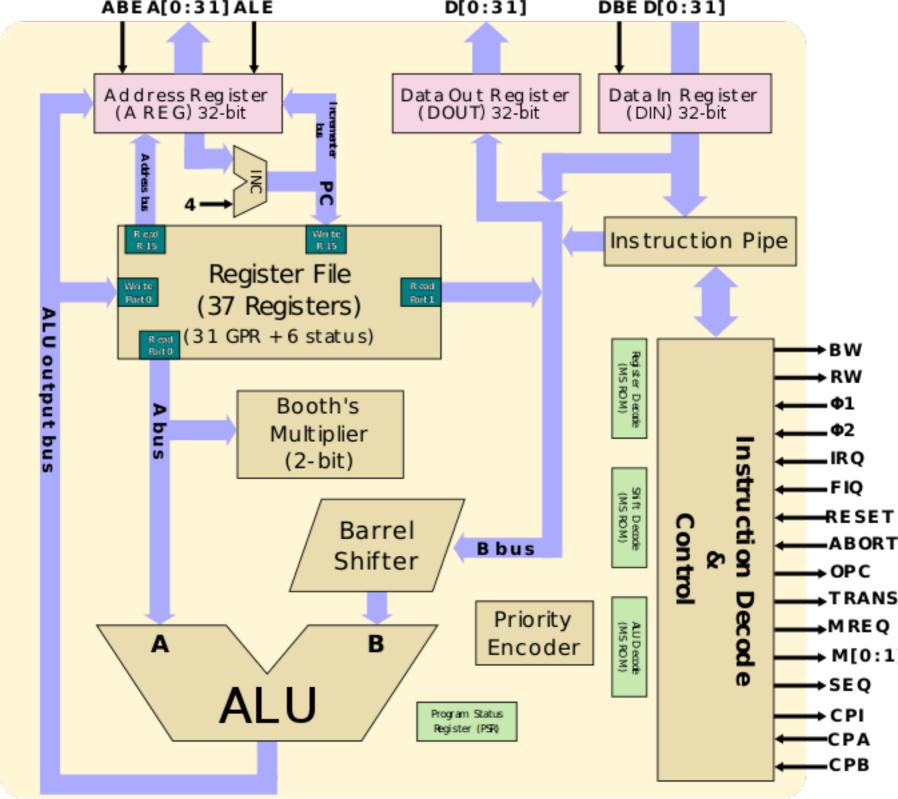

#### Processors implementing the ARMv3 - v6 ISA

(*Early ARM processors*) (∼ 1991-2004)

ARM6xx-ARM11xx

32-bit address bus 32-bit data buses

#### Processors implementing the ARMv7 – ARMv8 ISA

(ARM's Cortex processors) (Since 2004/2012)

Cortex lines

ARMv7: 32-bit ARMv8: 64-bit

with AArch64 and AArch32 modes

#### 4. Overview of ARM's Cortex-A series (5a)

Програмен модел на МП: Понятие за програмен модел. Режими. Регистри за обща употреба. Специализирани регистри. Флагове на регистъра за кода на условието (РКУ). Особености. Обзор на програмния модел на други МП.

There are a number of different processor modes. These are shown in the following table:

| Processor mode |            | le    | Description                                                                 |  |  |  |  |

|----------------|------------|-------|-----------------------------------------------------------------------------|--|--|--|--|

| 1              | User       | (usr) | the normal program execution mode                                           |  |  |  |  |

| 2              | FIQ        | (fiq) | designed to support a high-speed data transfer or channel process           |  |  |  |  |

| 3              | IRQ        | (irq) | used for general-purpose interrupt handling                                 |  |  |  |  |

| 4              | Supervisor | (svc) | a protected mode for the operating system                                   |  |  |  |  |

| 5              | Abort      | (abt) | used to implement virtual memory and/or memory protection                   |  |  |  |  |

| 6              | Undefined  | (und) | used to support software emulation of hardware coprocessors                 |  |  |  |  |

| 7              | System     | (sys) | used to run privileged operating system tasks (Architecture Version 4 only) |  |  |  |  |

Table 3-1: ARM processor modes

Mode changes may be made under software control or may be caused by external interrupts or exception processing. Most application programs will execute in User mode. The other modes, known as *privileged* modes, will be entered to service interrupts or exceptions or to access protected resources: see **©**3.10 Exceptions on page 3-12.

| User/<br>System | Supervi-<br>sor | Abort      | Undefined  | Interrupt | Fast<br>interrupt |

|-----------------|-----------------|------------|------------|-----------|-------------------|

| R0              | R0              | R0         | R0         | R0        | R0                |

| R1              | R1              | R1         | R1         | R1        | R1                |

| R2              | R2              | R2         | R2         | R2        | R2                |

| R3              | R3              | R3         | R3         | R3        | R3                |

| R4              | R4              | R4         | R4         | R4        | R4                |

| R5              | R5              | R5         | R5         | R5        | R5                |

| R6              | R6              | R6         | R6         | R6        | R6                |

| R7              | R7              | R7         | R7         | R7        | R7                |

| R8              | R8              | R8         | R8         | R8        | R8_FIQ            |

| R9              | R9              | R9         | R9         | R9        | R9_FIQ            |

| R10             | R10             | R10        | R10        | R10       | R10_FIQ           |

| R11             | R11             | R11        | R11        | R11       | R11_FIQ           |

| R12             | R12             | R12        | R12        | R12       | R12_FIQ           |

| R13             | R13_SVC         | R13_ABORT  | R13_UNDEF  | R13_IRQ   | R13_FIQ           |

| R14             | R14_SVC         | R14_ABORT  | R14_UNDEF  | R14_IRQ   | R14_FIQ           |

| PC              | PC              | PC         | PC         | PC        | PC                |

|                 |                 |            |            |           |                   |

| CPSR            | CPSR            | CPSR       | CPSR       | CPSR      | CPSR              |

| •               | SPSR_SVC        | SPSR_ABORT | SPSR_UNDEF | SPSR_IRQ  | SPSR_FIQ          |

Table 3-2: The ARM register set

Registers 0-12 are always free for general-purpose use. Registers 13 and 14, although available for general use, also have specific roles:

- Register 13 (also known as the *Stack Pointer* or SP) is banked across all modes to provide a private Stack Pointer for each mode (except System mode which shares the user mode R13).

- Register 14 (also known as the *Link Register* or LR) is used as the subroutine return address link register. R14 is also banked across all modes (except System mode which shares the user mode R14).

When a Subroutine call (Branch and Link instruction) is executed, R14 is set to the subroutine return address. The banked registers R14\_SVC, R14\_IRQ, R14\_FIQ, R14\_ABORT and R14\_UNDEF are used similarly to hold the return address when exceptions occur (or a subroutine return address if subroutine calls are executed within interrupt or exception routines). R14 may be treated as a general-purpose register at all other times.

Register 15 is used specifically to hold the *Program Counter* (PC). When R15 is read, bits [1:0] are zero and bits [31:2] contain the PC. When R15 is written bits[1:0] are ignored and bits[31:2] are written to the PC. Depending on how it is used, the value of the PC is either the address of the instruction plus *n* (where *n* is 8 for ARM state and 4 for Thumb state) or is unpredictable.

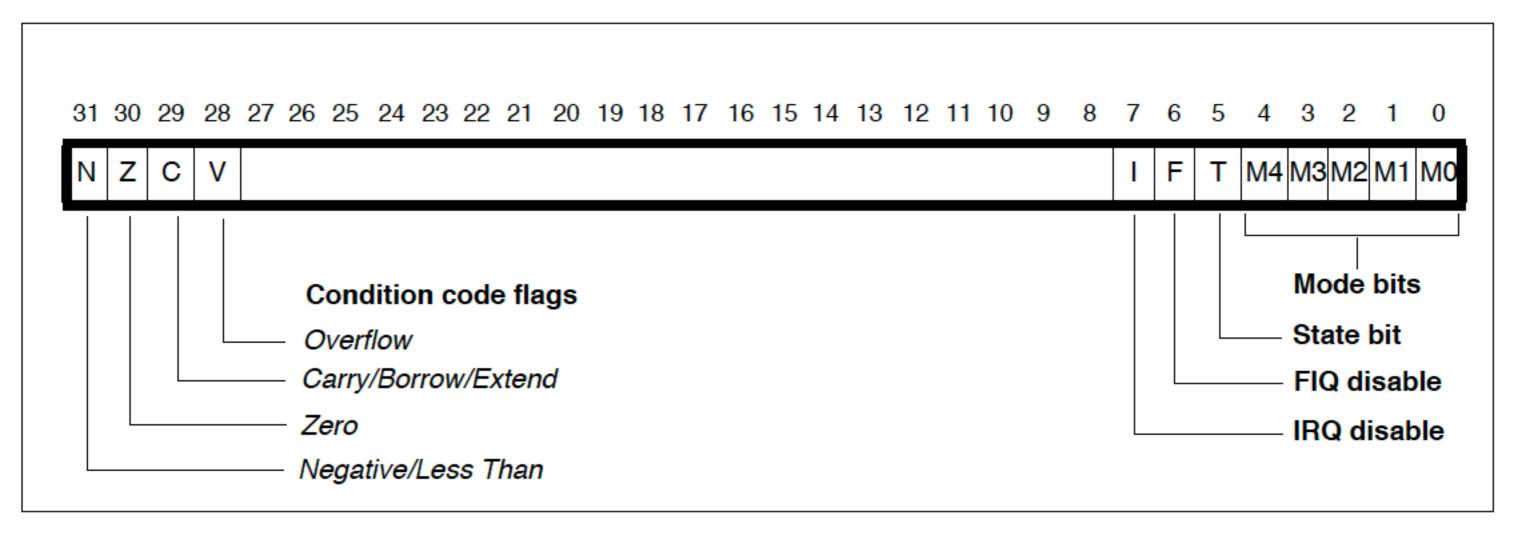

CPSR is the Current Program Status Register. This is accessible in all processor modes, and contains the condition code flags, interrupt enable flags, and current processor mode. In Architecture 4T, the CPSR also holds the processor state. See ◆3.9 Program Status Registers on page 3-10 for more information.

Процесорната фамилия ARM (Advanced RISC Machines) се състои от RISC микропроцесори, които имат 16 регистъра (фиг. 12.1) с общо предназначение с имена от R0 до R15. Регистрите са 32-битови. Те могат да съдържат както адреси, така и данни. Последният регистър R15 се използва за програмен брояч (PC), а регистър R13 служи за организиране на програмен стек (SP). Регистър R14 (LR) се използва като регистър, съдържащ адреса за връщане след подпрограма. Регистрите могат да се използват за съхранение на 8, 16 и 32-битови числа.

| <b> бит</b> 31           | <b></b> бит 0 |

|--------------------------|---------------|

| R0                       |               |

| R1                       |               |

| R2                       |               |

| R3                       |               |

| R4                       |               |

| R5                       |               |

| R6                       |               |

| R7                       |               |

| R8                       |               |

| R9                       |               |

| R10                      |               |

| R11                      |               |

| R12                      |               |

| R13 (Stack pointer – SP) |               |

| R14 (link register – LR) |               |

| R15 (PC)                 |               |

Фигура 12.1. Регистри на процесора ARM

Figure 3-4: Program Status Register format

#### The condition code flags

The N, Z, C and V (Negative, Zero, Carry and oVerflow) bits are collectively known as the condition code flags. The condition code flags in the CPSR can be changed as a result of arithmetic and logical operations in the processor, and can be tested by all ARM instructions to determine if the instruction is to be executed. All ARM instructions may be executed conditionally

The bottom 8 bits of a PSR (incorporating I, F, T and M[4:0]) are known collectively as the control bits. These change when an exception arises, and can be altered by software only when the processor is in a privileged mode.

| Interrupt disable bits | The I and F bits are the <i>interrupt disable bits</i> . When set, these disable the IRQ and FIQ interrupts respectively.                 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| The state bit          | Bit T is the processor state bit. When the state bit is set to 0, this indicates that the processor is in ARM state (ie. executing 32-bit |

The state bit is only implemented on Thumb-aware processors (Architecture 4T). On non Thumb-aware processors the state bit will always be zero.

processor is in Thumb state (executing 16-bit Thumb instructions)

ARM instructions). When it is set to 1, this indicates that the

The mode bits

The M4, M3, M2, M1 and M0 bits (M[4:0]) are the *mode bits*. These determine the mode in which the processor operates, as shown in **D** Table 3-4: The mode bits, below. Not all combinations of the mode bits define a valid processor mode. Only those explicitly described can be used.

.

| M[4:0] | Mode   | Accessible Registers                            |

|--------|--------|-------------------------------------------------|

| 10000  | User   | PC, R14 to R0, CPSR                             |

| 10001  | FIQ    | PC, R14_fiq to R8_fiq, R7 to R0, CPSR, SPSR_fiq |

| 10010  | IRQ    | PC, R14_irq, R13_irq,R12 to R0, CPSR, SPSR_irq  |

| 10011  | SVC    | PC, R14_svc, R13_svc,R12 to R0, CPSR, SPSR_svc  |

| 10111  | Abort  | PC, R14_abt, R13_abt,R12 to R0, CPSR, SPSR_abt  |

| 11011  | Undef  | PC, R14_und, R13_und,R12 to R0, CPSR, SPSR_und  |

| 11111  | System | PC, R14 to R0, CPSR (Architecture 4 only)       |

#### Преносът при изваждане е инверсен!

В много микропроцесори се използва този трик – изваждането да се извършва като събиране с инверсната стойност на умалителя плюс лог. 1 на входа за пренос. Така преносът се получава инвертиран на изхода за пренос на суматора. А ако следващата команда е изваждане с пренос (SBC), то тази команда изважда инверсията на преноса. По-подробно развито, ако има пренос, изваждането се свежда отново да събиране с инверсната стойност на умалителя плюс лог. 1 на входа за пренос на суматора, тъй като инвесията на преноса е лог. 0. А ако пренос няма, то от тази лог. 1 се изважда лог. 1 (инверсията на преноса) и така на входа за пренос на суматора ще има лог. О. На практика това означава, че на втория вход на суматора се подава инверсията на умалителя (получена от инверсните изходи на тригерите от регистъра, където се пази той), а на входа му за пренос – преносът от предходното така извършено изваждане. Така е и при "ARM".

| 31 | General-Purpose Registers    | 0        |

|----|------------------------------|----------|

|    |                              | EAX      |

|    |                              | EBX      |

|    |                              | ECX      |

|    |                              | EDX      |

|    |                              | ESI      |

|    |                              | EDI      |

|    |                              | EBP      |

|    |                              | ESP      |

|    | Segment Registers            | s<br>0   |

|    |                              | cs       |

|    |                              | DS       |

|    |                              | ss       |

|    |                              | ES       |

|    |                              | FS       |

|    |                              | GS       |

| 31 | Status and Control Registers | <u>o</u> |

|    |                              | _ EFLAGS |

| 31 |                              | <u>0</u> |

|    |                              | EIP      |

#### General-Purpose Registers

| 31 | 16 | 15 8 | 7    | 0 | 16-bit | 32-bit |

|----|----|------|------|---|--------|--------|

|    |    | AH   | AL   |   | AX     | EAX    |

|    |    | ВН   | BL   |   | BX     | EBX    |

|    |    | CH   | CL   |   | CX     | ECX    |

|    |    | DH   | DL   |   | DX     | EDX    |

|    |    | В    | Р    |   |        | EBP    |

|    |    | S    | SI . |   |        | ESI    |

|    |    | D    | )    |   |        | EDI    |

|    |    | S    | iP   |   |        | ESP    |

|    |    |      |      |   |        |        |

Figure 3-4. Alternate General-Purpose Register Names

#### Предимства на ARM пред x86

Архитектурата ARM е RISC и е създадена по-късно от x86, която е CISC. Въпреки това, следните предимства правят програмите за ARM по-кратки от тези за 80x86:

- 1. Наличието на *13 регистъра* за обща употреба срещу 7 за 80х86.

- 2. Наличието на *3 до 4 операнда* на команда при аритметично-логическите операции срещу 2 за 80х86 и дори само 1 за умножението и деленето (вярно е, че командата *IMUL* (80186+) има 3-операнден вариант, а някои нови FMA4- и XOP-команди имат до 5 операнда, но те са рядко срещани, специализирани и сложни).

- 3. Възможността всяка команда да бъде направена условна.

- 4. Възможността за избор дали командата да променя флаговете или не.

- 5. Възможността да се работи с изместено копие на десния операнд.

- 6. Ортогоналният набор от команди и адресни режими (на 80х86 е неортогонален).

#### Недостатъци на ARM спрямо x86

- 1. Няма трикомпонентен адресен режим (с 2 адресни регистъра плюс отместване-константа), какъвто има при х86.

- 2. Няма команда, която да променя флаг Z, без да променя флаг C. Това затруднява запазването на преноса между итерациите на цикъла.

- 3. Няма команда за размяна на съдържанието на 2 регистъра.

- 4. Няма команда за получаване на остатъка от целочислено делене.

- 5. Флагът С получава инверсна стойност след изваждане и сравнение, защото в ARM няма субтрактор; има само суматор. (Но това е по-скоро особеност, отколкото недостатък.)

# Figure 4.1 CPU Registers for MIPS32

| ·                         |                           |

|---------------------------|---------------------------|

| PC                        | 3.1                       |

| 31 0                      | r30                       |

|                           | r29                       |

|                           | r28                       |

|                           | r27                       |

|                           | r26                       |

|                           | r25                       |

|                           | r24                       |

|                           | r23                       |

|                           | r22                       |

|                           | r21                       |

|                           | r20                       |

|                           | r19                       |

|                           | r18                       |

|                           | r17                       |

|                           | r16                       |

|                           | r15                       |

|                           | r14                       |

|                           | r13                       |

|                           | r12                       |

|                           | r11                       |

|                           | r10                       |

|                           | r9                        |

|                           | r8                        |

|                           | r7                        |

|                           | ъ                         |

|                           | r5                        |

|                           | r4                        |

|                           | r3                        |

|                           | r2                        |

| OT                        | rl                        |

| IH                        | r0 (hardwired to zero)    |

| 31 0                      | 31 0                      |

| Special Purpose Registers | General Purpose Registers |

|                           |                           |

## USER MODEL (UISA)

#### Registers General-Purpose

GPR1 (64/32) GPR0 (64/32)

GPR31 (64/32)

## Floating-Point Registers

FPR1 (64) FPR0 (64)

FPR31 (64)

## Condition Register<sup>1</sup>

CR (32)

**IBATxU (32)**

SPR xxx

IBATxL (32)

SPR xxx

DBATxL (32)

DBATxU (32)

SPR xxx

SPR xxx

## Floating-Point Status and Control Register<sup>1</sup>

**FPSCR (32)**

### XER Register

XER (64/32) SPR 1

### Link Register

LR (64/32) SPR 8

### Count Register

CTR (64/32) SPR 9

### **USER MODEL**

Time Base Facility <sup>1</sup> (For Reading)

TBU (32) TBL (32) TBR 269 **TBR 268**

### Register (Optional) Processor Identification

PR SPR 1023

Machine State Register

Configuration Registers

SUPERVISOR MODEL -

OEA

MSR (64/32)

Processor Version Register PVR (32) (Read Only) **SPR 287**

## Memory Management Registers

Instruction BAT Registers 2,4

IBAT0U (32) IBAT0L (32) SPR 529 **SPR 528**

Data BAT Registers <sup>2,4</sup>

DBAT0U (32) **DBAT0L (32)** SPR 537 SPR 536

Segment Registers 1, 2

SR0 (32)

SDR1

SDR1 (64/32)

SPR 25

SR1 (32)

SR15 (32)

Address Space Register <sup>3</sup>

ASR (64)

SPR 280

## Exception Handling Registers

## Data Address Register

DAR (64/32) **SPR 19**

SPRGs

SPRG1 (64/32) SPRG0 (64/32) SPR 272 **SPR 273**

SPRG2 (64/32) SPR 275 SPR 274

SPRG3 (64/32)

Save and Restore Registers

DSISR (32)

**SPR 18**

DSISR 1

SRR1 (64/32) SRR0 (64/32) **SPR 27** SPR 26

Cause Register (Optional) Floating-Point Exception

**FPECR** SPR 1022

## Miscellaneous Registers

Time Base Facility <sup>1</sup> (For Writing)

TBU (32) TBL (32) **SPR 284** SPR 285

Decrementer <sup>1</sup>

DEC (32) **SPR 22**

> Data Address Breakpoint Register (Optional)

DABR (64/32) SPR 1013

External Access Register (Optional)

EAR (32) **SPR 282**

- These registers are 32-bit registers only.

- These registers are on 32-bit implementations only.

- ω These registers are on 64-bit implementations only

- These registers are implementation dependent

- 64-bit registers operating in 32-bit mode clear the high order 32-bits.

- The ARM instruction set can be divided into six broad classes of instruction:

- Branch instructions

- Data-processing instructions on page A1-7

- Status register transfer instructions on page A1-8

- Load and store instructions on page A1-8

- Coprocessor instructions on page A1-10

- Exception-generating instructions on page A1-10.

Most data-processing instructions and one type of coprocessor instruction can update the four condition code flags in the CPSR (Negative, Zero, Carry and oVerflow) according to their result.

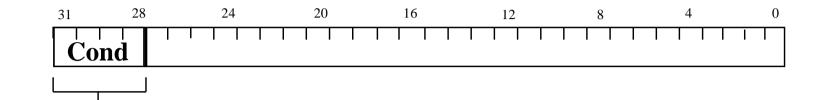

Almost all ARM instructions contain a 4-bit *condition* field. One value of this field specifies that the instruction is executed unconditionally.

Fourteen other values specify *conditional execution* of the instruction. If the condition code flags indicate that the corresponding condition is true when the instruction starts executing, it executes normally. Otherwise, the instruction does nothing. The 14 available conditions allow:

- tests for equality and non-equality

- tests for <, <=, >, and >= inequalities, in both signed and unsigned arithmetic

- each condition code flag to be tested individually.

The sixteenth value of the condition field encodes alternative instructions. These do not allow conditional execution. Before ARMv5 these instructions were UNPREDICTABLE.

#### **ARM Instruction Set Format**

| 31 28        | 27             |     |     |     | 16      | 515 87  |               |       | 0         |

|--------------|----------------|-----|-----|-----|---------|---------|---------------|-------|-----------|

| Cond         | 0010           | pco | ode | S   | Rn      | Rd      | Operand2      |       |           |

| Cond         | 0 0 0 0        | 0   | 0 7 | A S | Rd      | Rn      | Rs            | 1 0 0 | 1 Rm      |

| Cond         | 0 0 0 0        | 1   | U A | A S | RdHi    | RdLo    | Rs            | 1 0 0 | 1 Rm      |

| Cond         | 0 0 0 1        | 0   | в   | 0   | Rn      | Rd      | 0 0 0 0       | 1 0 0 | 1 Rm      |

| Cond         | Cond 0 1 I P U |     |     |     | Rn      | Rd      | Offset        |       |           |

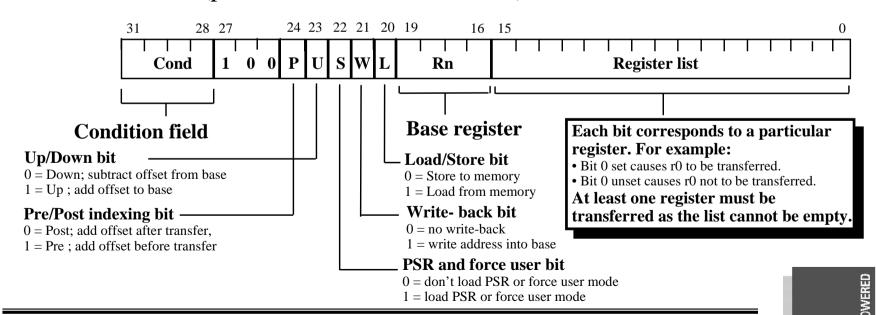

| Cond         | 1 0 0 P        | U   | s v | I L | Rn      |         | Register List |       |           |

| Cond         | 0 0 0 F        | U   | 1 7 | V L | Rn      | Rd      | Offset1       | 1 S H | 1 Offset2 |

| Cond         | 0 0 0 P        | Ū   | 0 7 | L   | Rn      | Rd      | 0 0 0 0       | 1 S H | 1 Rm      |

| Cond 1 0 1 L |                |     |     |     |         | Offs    | set           |       |           |

| Cond 0 0 0 1 |                |     | 0   | 1 0 | 1 1 1 1 | 1 1 1 1 | 1 1 1 1       | 0 0 0 | 1 Rn      |

| Cond         | 1 1 0 F        | U   | И   | v L | Rn      | CRd     | CPNum         | Of    | fset      |

| Cond         | ond 1110       |     | Opi |     | CRn     | CRd     | CPNum         | Op2   | 0 CRm     |

| Cond         | 1 1 1 0        |     | )p1 | L   | CRn     | Rd      | CPNum         | Op2   | 1 CRm     |

| Cond 1 1 1 1 |                |     |     |     |         | SWI Nu  | ımber         |       |           |

#### **Instruction type**

Data processing / PSR Transfer

Multiply

Long Multiply (v3M / v4 only)

Swap

Load/Store Byte/Word

Load/Store Multiple

Halfword transfer : Immediate offset (v4 only)

Halfword transfer: Register offset (v4 only)

Branch

Branch Exchange (v4T only)

Coprocessor data transfer

Coprocessor data operation

Coprocessor register transfer

Software interrupt

#### **Conditional Execution**

- \* Most instruction sets only allow branches to be executed conditionally.

- \* However by reusing the condition evaluation hardware, ARM effectively increases number of instructions.

- All instructions contain a condition field which determines whether the CPU will execute them.

- Non-executed instructions soak up 1 cycle.

- Still have to complete cycle so as to allow fetching and decoding of following instructions.

- \* This removes the need for many branches, which stall the pipeline (3 cycles to refill).

- Allows very dense in-line code, without branches.

- The Time penalty of not executing several conditional instructions is frequently less than overhead of the branch or subroutine call that would otherwise be needed.

#### The Condition Field

0001 = NE - Z clear (not equal)

0010 = HS / CS - C set (unsigned higher or same)

0011 = LO / CC - C clear (unsigned lower)

0100 = MI - N set (negative)

0101 = PL - N clear (positive or zero)

0110 = VS - V set (overflow)

0111 = VC - V clear (no overflow)

1000 = HI - C set and Z clear (unsigned higher)

1001 = LS - C clear or Z (set unsigned lower or same)

1010 = GE - N set and V set, or N clear and V clear (>or =)

1011 = LT - N set and V clear, or N clear and V set (>)

1100 = GT - Z clear, and either N set and V set, or N clear and V set (>)

1101 = LE - Z set, or N set and V clear, or N clear and V set (<, or =)

1110 = AL - always

1111 = NV - reserved.

### Using and updating the Condition Field

- \* To execute an instruction conditionally, simply postfix it with the appropriate condition:

- For example an add instruction takes the form:

```

- ADD r0, r1, r2  ; r0 = r1 + r2 (ADDAL)

```

• To execute this only if the zero flag is set:

```

- ADDEQ r0,r1,r2 ; If zero flag set then...

; ... r0 = r1 + r2

```

- \* By default, data processing operations do not affect the condition flags (apart from the comparisons where this is the only effect). To cause the condition flags to be updated, the S bit of the instruction needs to be set by postfixing the instruction (and any condition code) with an "S".

- For example to add two numbers and set the condition flags:

```

- ADDS r0,r1,r2 ; r0 = r1 + r2 ; ... and set flags

```

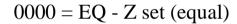

#### **Branch instructions (1)**

- \* **Branch:** B{<cond>} label

- \* Branch with Link: BL{<cond>} sub\_routine\_label

- \* The offset for branch instructions is calculated by the assembler:

- By taking the difference between the branch instruction and the target address minus 8 (to allow for the pipeline).

- This gives a 26 bit offset which is right shifted 2 bits (as the bottom two bits are always zero as instructions are word aligned) and stored into the instruction encoding.

- This gives a range of  $\pm$  32 Mbytes.

#### **Branch instructions (2)**

- \* When executing the instruction, the processor:

- shifts the offset left two bits, sign extends it to 32 bits, and adds it to PC.

- \* Execution then continues from the new PC, once the pipeline has been refilled.

- \* The "Branch with link" instruction implements a subroutine call by writing PC-4 into the LR of the current bank.

- i.e. the address of the next instruction following the branch with link (allowing for the pipeline).

- \* To return from subroutine, simply need to restore the PC from the LR:

- MOV pc, lr

- Again, pipeline has to refill before execution continues.

- \* The "Branch" instruction does not affect LR.

- \* Note: Architecture 4T offers a further ARM branch instruction, BX

- See Thumb Instruction Set Module for details.

#### Data processing Instructions

- \* Largest family of ARM instructions, all sharing the same instruction format.

- \* Contains:

- Arithmetic operations

- Comparisons (no results just set condition codes)

- Logical operations

- Data movement between registers

- \* Remember, this is a load / store architecture

- These instruction only work on registers, *NOT* memory.

- \* They each perform a specific operation on one or two operands.

- First operand always a register Rn

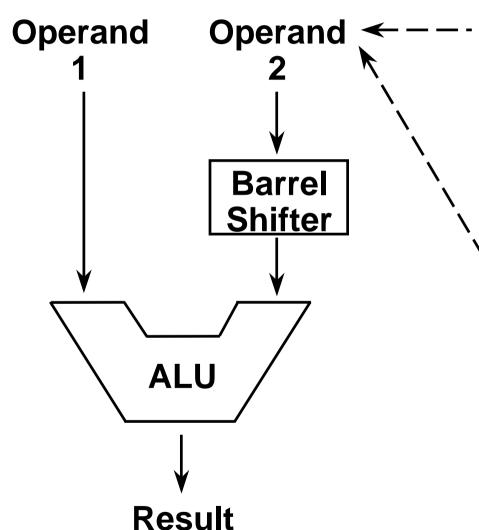

- Second operand sent to the ALU via barrel shifter.

- \* We will examine the barrel shifter shortly.

#### **Arithmetic Operations**

#### \* Operations are:

- ADD operand1 + operand2

- ADC operand1 + operand2 + carry

- SUB operand1 operand2

- SBC operand1 operand2 + carry -1

- RSB operand2 operand1

- RSC operand2 operand1 + carry 1

#### \* Syntax:

• <Operation>{<cond>}{S} Rd, Rn, Operand2

#### \* Examples

- ADD r0, r1, r2

- SUBGT r3, r3, #1

- RSBLES r4, r5, #5

#### Comparisons

- \* The only effect of the comparisons is to

- *UPDATE THE CONDITION FLAGS*. Thus no need to set S bit.

- \* Operations are:

- CMP operand1 operand2, but result not written

- CMN operand1 + operand2, but result not written

- TST operand1 AND operand2, but result not written

- TEQ operand1 EOR operand2, but result not written

- \* Syntax:

- <Operation>{<cond>} Rn, Operand2

- \* Examples:

- CMP r0, r1

- TSTEQ r2, #5

#### **Logical Operations**

- \* Operations are:

- AND operand1 AND operand2

- EOR operand1 EOR operand2

- ORR operand1 OR operand2

- BIC operand1 AND NOT operand2 [ie bit clear]

- \* Syntax:

- <Operation>{<cond>}{S} Rd, Rn, Operand2

- \* Examples:

- AND r0, r1, r2

- BICEQ r2, r3, #7

- EORS r1,r3,r0

#### **Data Movement**

- \* Operations are:

- MOV operand2

- MVN NOT operand2

Note that these make no use of operand1.

- \* Syntax:

- <Operation>{<cond>}{S} Rd, Operand2

- \* Examples:

- MOV r0, r1

- MOVS r2, #10

- MVNEQ r1,#0

#### Quiz #2

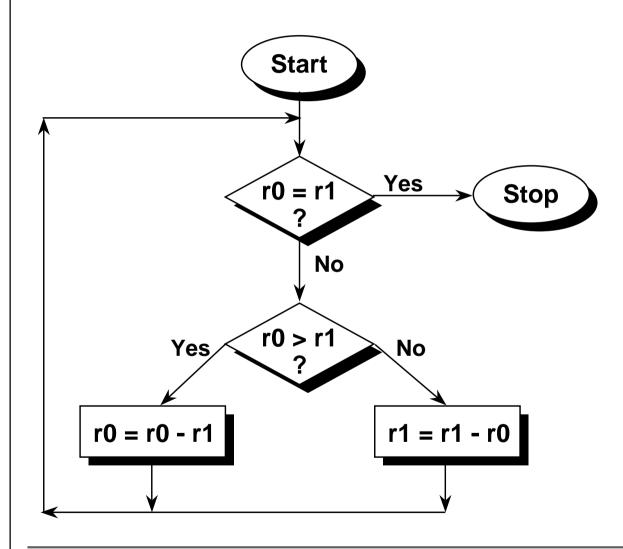

- \* Convert the GCD algorithm given in this flowchart into

- 1) "Normal" assembler, where only branches can be conditional.

- 2) ARM assembler, where all instructions are conditional, thus improving code density.

- \* The only instructions you need are CMP, B and SUB.

#### **Quiz #2 - Sample Solutions**

#### "Normal" Assembler

```

gcd cmp r0, r1 ;reached the end?

beq stop

blt less ;if r0 > r1

sub r0, r0, r1 ;subtract r1 from r0

bal gcd

less sub r1, r1, r0 ;subtract r0 from r1

bal gcd

stop

```

#### **ARM Conditional Assembler**

```

gcd cmp r0, r1 ;if r0 > r1

subgt r0, r0, r1 ;subtract r1 from r0

sublt r1, r1, r0 ;else subtract r0 from r1

bne gcd ;reached the end?

```

#### **The Barrel Shifter**

- \* The ARM doesn't have actual shift instructions.

- \* Instead it has a barrel shifter which provides a mechanism to carry out shifts as part of other instructions.

- \* So what operations does the barrel shifter support?

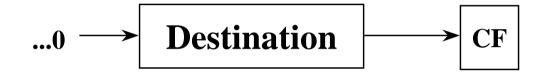

#### **Barrel Shifter - Left Shift**

\* Shifts left by the specified amount (multiplies by powers of two) e.g.

LSL #5 = multiply by 32

#### **Logical Shift Left (LSL)**

#### **Barrel Shifter - Right Shifts**

#### **Logical Shift Right**

•Shifts right by the specified amount (divides by powers of two) e.g.

LSR #5 = divide by 32

#### Arithmetic Shift Right

•Shifts right (divides by powers of two) and preserves the sign bit, for 2's complement operations. e.g.

ASR #5 = divide by 32

**Logical Shift Right**

**Arithmetic Shift Right**

Sign bit shifted in

#### **Barrel Shifter - Rotations**

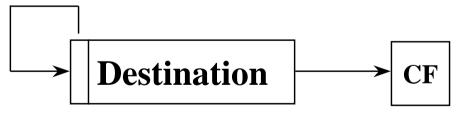

#### **Rotate Right (ROR)**

• Similar to an ASR but the bits wrap around as they leave the LSB and appear as the MSB.

**e.g.** ROR #5

• Note the last bit rotated is also used as the Carry Out.

# Rotate Right Destination CF

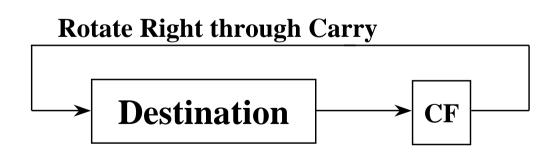

#### **Rotate Right Extended (RRX)**

- This operation uses the CPSR C flag as a 33rd bit.

- Rotates right by 1 bit. Encoded as ROR #0.

# **Using the Barrel Shifter: The Second Operand**

- \* Register, optionally with shift operation applied.

- \* Shift value can be either be:

- 5 bit unsigned integer

- Specified in bottom byte of another register.

#### \* Immediate value

- 8 bit number

- Can be rotated right through an even number of positions.

- Assembler will calculate rotate for you from constant.

# Second Operand : Shifted Register

- \* The amount by which the register is to be shifted is contained in either:

- the immediate 5-bit field in the instruction

- NO OVERHEAD

- Shift is done for free executes in single cycle.

- the bottom byte of a register (not PC)

- Then takes extra cycle to execute

- ARM doesn't have enough read ports to read 3 registers at once.

- Then same as on other processors where shift is separate instruction.

- \* If no shift is specified then a default shift is applied: LSL #0

- i.e. barrel shifter has no effect on value in register.

# Second Operand: Using a Shifted Register

- \* Using a multiplication instruction to multiply by a constant means first loading the constant into a register and then waiting a number of internal cycles for the instruction to complete.

- \* A more optimum solution can often be found by using some combination of MOVs, ADDs, SUBs and RSBs with shifts.

- Multiplications by a constant equal to a ((power of 2)  $\pm$  1) can be done in one cycle.

```

* Example: r0 = r1 * 5

Example: r0 = r1 + (r1 * 4)

ï ADD r0, r1, r1, LSL #2

```

```

* Example: r2 = r3 * 105

Example: r2 = r3 * 15 * 7

Example: r2 = r3 * (16 - 1) * (8 - 1)

ï RSB r2, r3, r3, LSL #4 ; r2 = r3 * 15

ï RSB r2, r2, r2, LSL #3 ; r2 = r2 * 7

```

# Second Operand: Immediate Value (1)

- \* There is no single instruction which will load a 32 bit immediate constant into a register without performing a data load from memory.

- All ARM instructions are 32 bits long

- ARM instructions do not use the instruction stream as data.

- \* The data processing instruction format has 12 bits available for operand2

- If used directly this would only give a range of 4096.

- \* Instead it is used to store 8 bit constants, giving a range of 0 255.

- \* These 8 bits can then be rotated right through an even number of positions (ie RORs by 0, 2, 4,...30).

- This gives a much larger range of constants that can be directly loaded, though some constants will still need to be loaded from memory.

# Second Operand: Immediate Value (2)

- \* This gives us:

- 0 255

[0 - 0xff]

• 256,260,264,..,1020

- [0x100-0x3fc, step 4, 0x40-0xff ror 30]

- 1024,1040,1056,..,4080

- [0x400-0xff0, step 16, 0x40-0xff ror 28]

- 4096,4160, 4224,...,16320

- [0x1000-0x3fc0, step 64, 0x40-0xff ror 26]

- \* These can be loaded using, for example:

- MOV r0, #0x40, 26

- ; => MOV r0, #0x1000 (ie 4096)

- \* To make this easier, the assembler will convert to this form for us if simply given the required constant:

- MOV r0, #4096

- ; => MOV r0, #0x1000 (ie 0x40 ror 26)

- \* The bitwise complements can also be formed using MVN:

- MOV r0, #0xFFFFFFF

- ; assembles to MVN r0, #0

- \* If the required constant cannot be generated, an error will be reported.

### Loading full 32 bit constants

- \* Although the MOV/MVN mechansim will load a large range of constants into a register, sometimes this mechansim will not generate the required constant.

- \* Therefore, the assembler also provides a method which will load ANY 32 bit constant:

- LDR rd,=numeric constant

- \* If the constant can be constructed using either a MOV or MVN then this will be the instruction actually generated.

- \* Otherwise, the assembler will produce an LDR instruction with a PC-relative address to read the constant from a literal pool.

- LDR r0,=0x42 ; generates MOV r0,#0x42

- LDR r0,=0x55555555; generate LDR r0,[pc, offset to lit pool]

- \* As this mechanism will always generate the best instruction for a given case, it is the recommended way of loading constants.

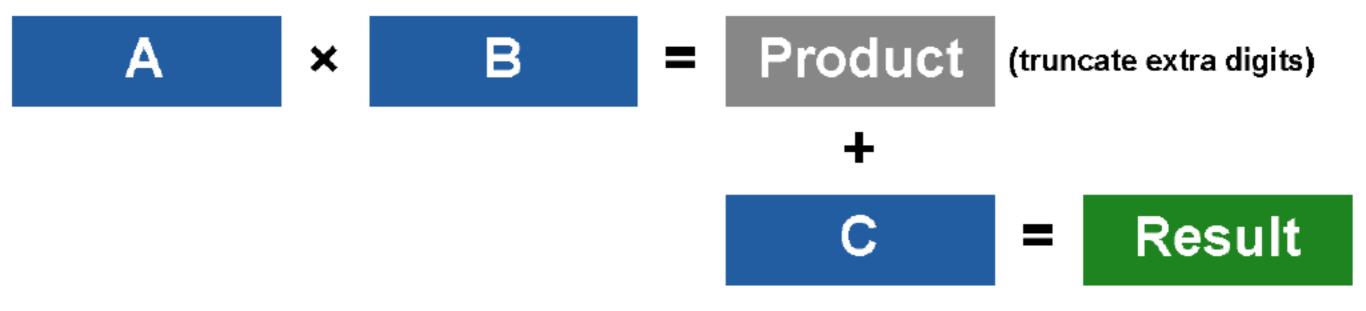

## Multiplication Instructions

- The Basic ARM provides two multiplication instructions.

- Multiply

- $MUL\{\langle cond \rangle\}\{S\}\}$  Rd, Rm, Rs ; Rd = Rm \* Rs

- **Multiply Accumulate** does addition for free

- $MLA\{\langle cond \rangle\}\{S\}\ Rd, Rm, Rs, Rn$  ; Rd = (Rm \* Rs) + Rn

- **Restrictions on use:**

- Rd and Rm cannot be the same register

- Can be avoid by swapping Rm and Rs around. This works because multiplication is commutative.

- Cannot use PC.

These will be picked up by the assembler if overlooked.

- Operands can be considered signed or unsigned

- Up to user to interpret correctly.

## **Multiplication Implementation**

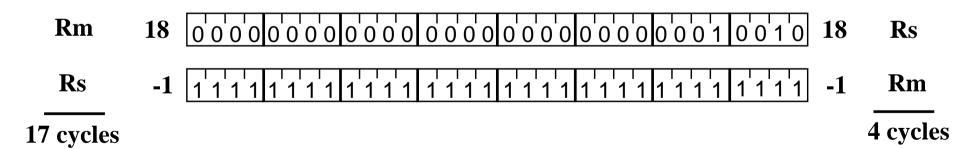

- \* The ARM makes use of Booth's Algorithm to perform integer multiplication.

- \* On non-M ARMs this operates on 2 bits of Rs at a time.

- For each pair of bits this takes 1 cycle (plus 1 cycle to start with).

- However when there are no more 1's left in Rs, the multiplication will early-terminate.

- \* Example: Multiply 18 and -1 : Rd = Rm \* Rs

\* Note: Compiler does not use early termination criteria to decide on which order to place operands.

### **Extended Multiply Instructions**

- \* M variants of ARM cores contain extended multiplication hardware. This provides three enhancements:

- An 8 bit Booth's Algorithm is used

- Multiplication is carried out faster (maximum for standard instructions is now 5 cycles).

- Early termination method improved so that now completes multiplication when all remaining bit sets contain

- all zeroes (as with non-M ARMs), or

- all ones.

Thus the previous example would early terminate in 2 cycles in both cases.

- 64 bit results can now be produced from two 32bit operands

- Higher accuracy.

- Pair of registers used to store result.

# Multiply-Long and Multiply-Accumulate Long

- \* Instructions are

- MULL which gives RdHi,RdLo:=Rm\*Rs

- MLAL which gives RdHi,RdLo:=(Rm\*Rs)+RdHi,RdLo

- \* However the full 64 bit of the result now matter (lower precision multiply instructions simply throws top 32bits away)

- Need to specify whether operands are signed or unsigned

- \* Therefore syntax of new instructions are:

- UMULL{<cond>}{S} RdLo,RdHi,Rm,Rs

- UMLAL{<cond>}{S} RdLo,RdHi,Rm,Rs

- SMULL{<cond>}{S} RdLo, RdHi, Rm, Rs

- SMLAL{<cond>}{S} RdLo, RdHi, Rm, Rs

- \* Not generated by the compiler.

Warning: Unpredictable on non-MARMs.

### Quiz #3

#### 1. Specify instructions which will implement the following:

a)

$$r0 = 16$$

b)

$$r1 = r0 * 4$$

c)

$$r0 = r1 / 16$$

(  $r1$  signed 2's comp.) d)  $r1 = r2 * 7$

d)

$$r1 = r2 * 7$$

#### 2. What will the following instructions do?

#### 3. What does the following instruction sequence do?

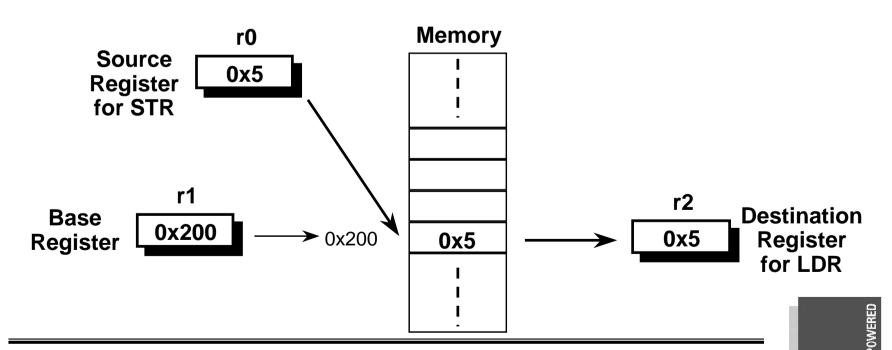

#### **Load / Store Instructions**

- \* The ARM is a Load / Store Architecture:

- Does not support memory to memory data processing operations.

- Must move data values into registers before using them.

- \* This might sound inefficient, but in practice isn't:

- Load data values from memory into registers.

- Process data in registers using a number of data processing instructions which are not slowed down by memory access.

- Store results from registers out to memory.

- \* The ARM has three sets of instructions which interact with main memory. These are:

- Single register data transfer (LDR / STR).

- Block data transfer (LDM/STM).

- Single Data Swap (SWP).

## Single register data transfer

- \* The basic load and store instructions are:

- Load and Store Word or Byte

- LDR / STR / LDRB / STRB

- \* ARM Architecture Version 4 also adds support for halfwords and signed data.

- Load and Store Halfword

- LDRH / STRH

- Load Signed Byte or Halfword load value and sign extend it to 32 bits.

- LDRSB / LDRSH

- \* All of these instructions can be conditionally executed by inserting the appropriate condition code after STR / LDR.

- e.g. LDREQB

- \* Syntax:

- <LDR|STR>{<cond>}{<size>} Rd, <address>

# Load and Store Word or Byte: Base Register

- \* The memory location to be accessed is held in a base register

- STR r0, [r1] ; Store contents of r0 to location pointed to

- ; by contents of r1.

- LDR r2, [r1] ; Load r2 with contents of memory location

- ; pointed to by contents of r1.

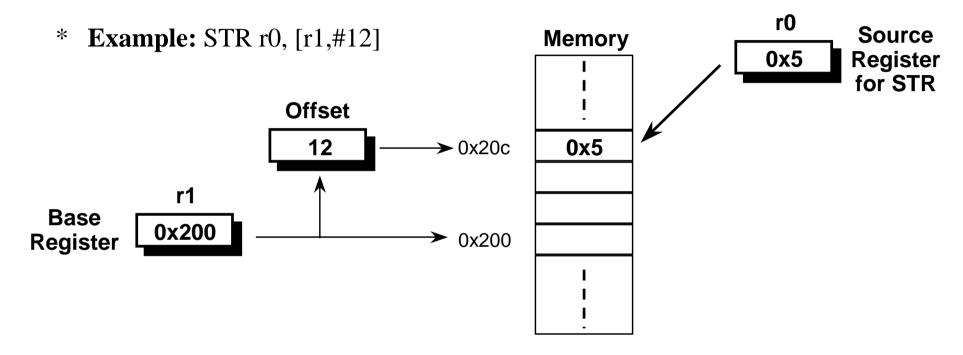

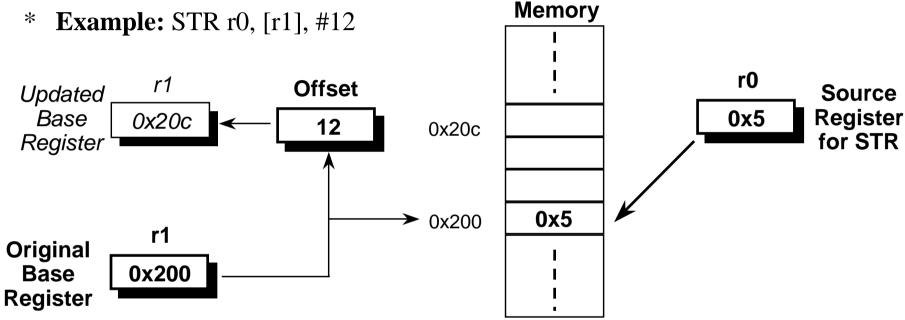

# Load and Store Word or Byte: Offsets from the Base Register

- \* As well as accessing the actual location contained in the base register, these instructions can access a location offset from the base register pointer.

- \* This offset can be

- An unsigned 12bit immediate value (ie 0 4095 bytes).

- A register, optionally shifted by an immediate value

- \* This can be either added or subtracted from the base register:

- Prefix the offset value or register with '+' (default) or '-'.

- \* This offset can be applied:

- before the transfer is made: *Pre-indexed addressing*

- <u>optionally</u> *auto-incrementing* the base register, by postfixing the instruction with an '!'.

- after the transfer is made: **Post-indexed addressing**

- causing the base register to be *auto-incremented*.

# Load and Store Word or Byte: Pre-indexed Addressing

- \* **To store to location 0x1f4 instead use:** STR r0, [r1,#-12]

- \* To auto-increment base pointer to 0x20c use: STR r0, [r1, #12]!

- \* If r2 contains 3, access 0x20c by multiplying this by 4:

- STR r0, [r1, r2, LSL #2]

# Load and Store Word or Byte: Post-indexed Addressing

- \* To auto-increment the base register to location 0x1f4 instead use:

- STR r0, [r1], #-12

- \* If r2 contains 3, auto-increment base register to 0x20c by multiplying this by 4:

- STR r0, [r1], r2, LSL #2

# Load and Stores with User Mode Privilege

- \* When using post-indexed addressing, there is a further form of Load/Store Word/Byte:

- <LDR|STR>{<cond>}{B}T Rd, <post\_indexed\_address>

- \* When used in a privileged mode, this does the load/store with user mode privilege.

- Normally used by an exception handler that is emulating a memory access instruction that would normally execute in user mode.

# **Example Usage of Addressing Modes**

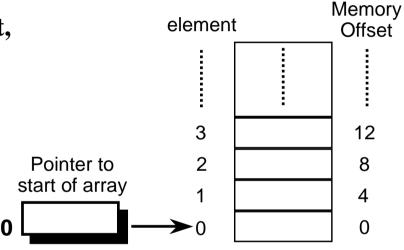

- \* Imagine an array, the first element of which is pointed to by the contents of r0.

- \* If we want to access a particular element, then we can use pre-indexed addressing:

- r1 is element we want.

- LDR r2, [r0, r1, LSL #2]

- \* If we want to step through every element of the array, for instance to produce sum of elements in the array, then we can use post-indexed addressing within a loop:

- r1 is address of current element (initially equal to r0).

- LDR r2, [r1], #4

Use a further register to store the address of final element, so that the loop can be correctly terminated.

# Offsets for Halfword and Signed Halfword / Byte Access

- \* The Load and Store Halfword and Load Signed Byte or Halfword instructions can make use of pre- and post-indexed addressing in much the same way as the basic load and store instructions.

- \* However the actual offset formats are more constrained:

- The immediate value is limited to 8 bits (rather than 12 bits) giving an offset of 0-255 bytes.

- The register form cannot have a shift applied to it.

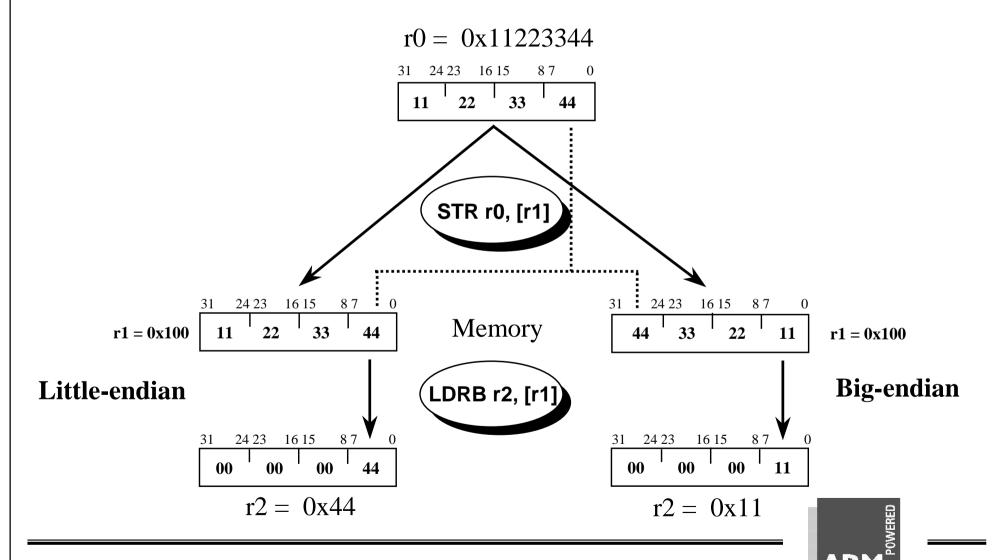

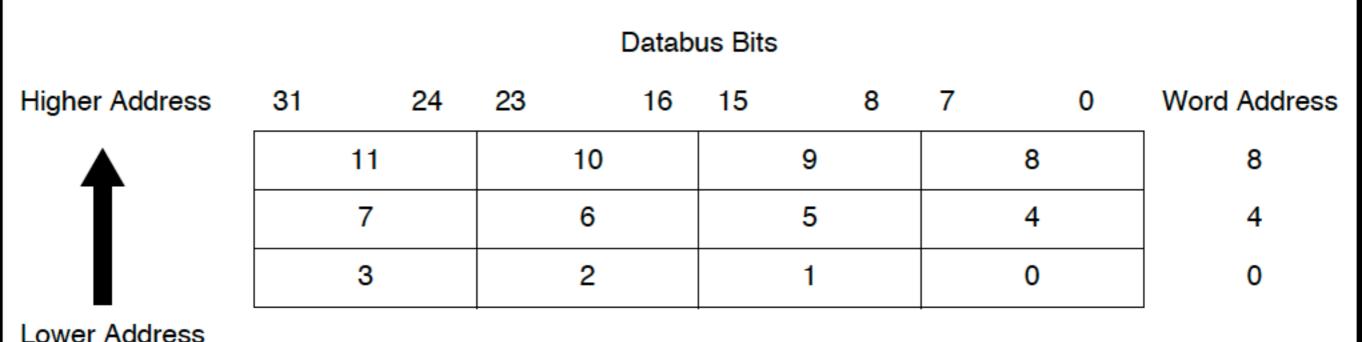

#### **Effect of endianess**

- \* The ARM can be set up to access its data in either little or big endian format.

- \* Little endian:

- Least significant byte of a word is stored in *bits 0-7* of an addressed word.

- \* Big endian:

- Least significant byte of a word is stored in *bits 24-31* of an addressed word.

- \* This has no real relevance unless data is stored as words and then accessed in smaller sized quantities (halfwords or bytes).

- Which byte / halfword is accessed will depend on the endianess of the system involved.

## **Endianess Example**

### Quiz #4

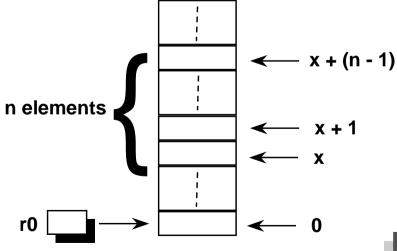

- \* Write a segment of code that add together elements x to x+(n-1) of an array, where the element x=0 is the first element of the array.

- \* Each element of the array is word sized (ie. 32 bits).

- \* The segment should use post-indexed addressing.

- \* At the start of your segments, you should assume that:

- r0 points to the start of the array.

- r1 = x

- r2 = n

#### **Elements**

### **Quiz #4 - Sample Solution**

```

ADD r0, r0, r1, LSL#2 ; Set r0 to address of element x

ADD r2, r0, r2, LSL#2

; Set r2 to address of element n+1

MOV r1, #0

: Initialise counter

loop

LDR r3, [r0], #4

: Access element and move to next

ADD r1, r1, r3

; Add contents to counter

CMP r0, r2

: Have we reached element x+n?

BLT loop

; If not - repeat for

next element

: on exit sum contained in r1

```

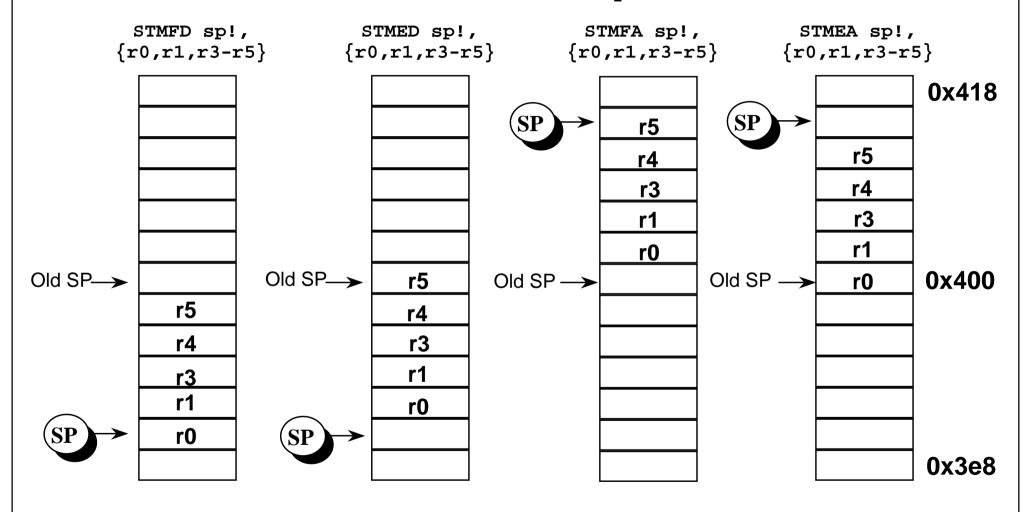

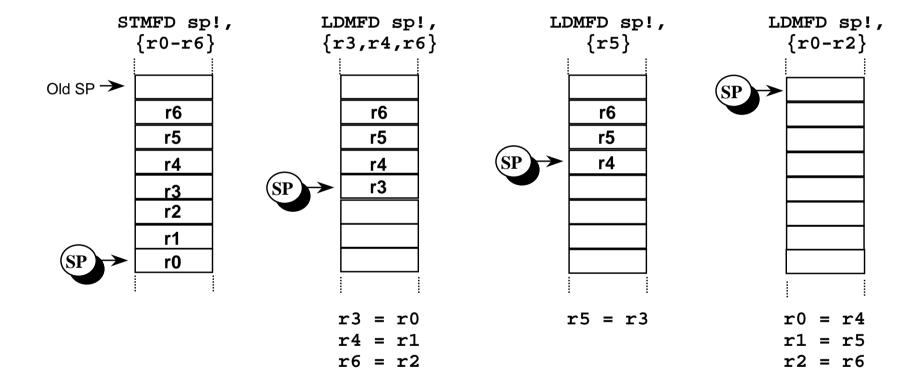

## **Block Data Transfer (1)**

- \* The Load and Store Multiple instructions (LDM / STM) allow betweeen 1 and 16 registers to be transferred to or from memory.

- \* The transferred registers can be either:

- Any subset of the current bank of registers (default).

- Any subset of the user mode bank of registers when in a priviledged mode (postfix instruction with a '^').

# **Block Data Transfer (2)**

- \* Base register used to determine where memory access should occur.

- 4 different addressing modes allow increment and decrement inclusive or exclusive of the base register location.

- Base register can be optionally updated following the transfer (by appending it with an '!'.

- Lowest register number is always transferred to/from lowest memory location accessed.

- \* These instructions are very efficient for

- Saving and restoring context

- For this useful to view memory as a stack.

- Moving large blocks of data around memory

- For this useful to directly represent functionality of the instructions.

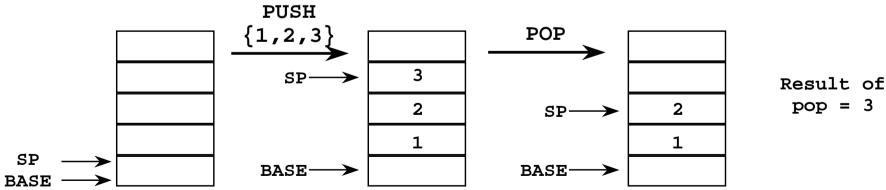

#### **Stacks**

- \* A stack is an area of memory which grows as new data is "pushed" onto the "top" of it, and shrinks as data is "popped" off the top.

- \* Two pointers define the current limits of the stack.

- A base pointer

- used to point to the "bottom" of the stack (the first location).

- A stack pointer

- used to point the current "top" of the stack.

ARM BOWERED

## **Stack Operation**

- \* Traditionally, a stack grows down in memory, with the last "pushed" value at the lowest address. The ARM also supports ascending stacks, where the stack structure grows up through memory.

- \* The value of the stack pointer can either:

- Point to the last occupied address (Full stack)

- and so needs pre-decrementing (ie before the push)

- Point to the next occupied address (Empty stack)

- and so needs post-decrementing (ie after the push)

- \* The stack type to be used is given by the postfix to the instruction:

- STMFD / LDMFD : Full Descending stack

- STMFA / LDMFA : Full Ascending stack.

- STMED / LDMED : Empty Descending stack

- STMEA / LDMEA : Empty Ascending stack

- \* Note: ARM Compiler will always use a Full descending stack.

### **Stack Examples**

#### Stacks and Subroutines

\* One use of stacks is to create temporary register workspace for subroutines. Any registers that are needed can be pushed onto the stack at the start of the subroutine and popped off again at the end so as to restore them before return to the caller:

```

STMFD sp!,{r0-r12, lr} ; stack all registers

.....; and the return address

.....

LDMFD sp!,{r0-r12, pc} ; load all the registers

; and return automatically

```

- \* See the chapter on the ARM Procedure Call Standard in the SDT Reference Manual for further details of register usage within subroutines.

- \* If the pop instruction also had the 'S' bit set (using '^') then the transfer of the PC when in a priviledged mode would also cause the SPSR to be copied into the CPSR (see exception handling module).

# Direct functionality of Block Data Transfer

- \* When LDM / STM are not being used to implement stacks, it is clearer to specify exactly what functionality of the instruction is:

- i.e. specify whether to increment / decrement the base pointer, before or after the memory access.

- \* In order to do this, LDM / STM support a further syntax in addition to the stack one:

- STMIA / LDMIA : Increment After

- STMIB / LDMIB : Increment Before

- STMDA / LDMDA : Decrement After

- STMDB / LDMDB : Decrement Before

### **Example: Block Copy**

• Copy a block of memory, which is an exact multiple of 12 words long from the location pointed to by r12 to the location pointed to by r13. r14 points to the end of block to be copied.

```

; r12 points to the start of the source data

; r14 points to the end of the source data

; r13 points to the start of the destination data

r13 →

qool

LDMIA

r12!, {r0-r11} ; load 48 bytes

r13!, {r0-r11}; and store them

STMIA

r14 \longrightarrow

Increasing

CMP

r12, r14; check for the end

Memory

qool

BNE

; and loop until done

• This loop transfers 48 bytes in 31 cycles

```

• Over 50 Mbytes/sec at 33 MHz

#### Quiz #5

- \* The contents of registers r0 to r6 need to be swapped around thus:

- r0 moved into r3

- r1 moved into r4

- r2 moved into r6

- r3 moved into r5

- r4 moved into r0

- r5 moved into r1

- r6 moved into r2

- \* Write a segment of code that uses full descending stack operations to carry this out, and hence requires no use of any other registers for temporary storage.

### **Quiz #5 - Sample Solution**

## Instruction Set

#### 4.5.5 Using R15 as an operand

If R15 (the PC) is used as an operand in a data processing instruction and the shift amount is instruction-specified, the PC value will be the address of the instruction plus 8 bytes.

For any register-controlled shift instructions, neither Rn nor Rm may be R15.

### Instruction set orthogonality

Instruction set orthogonality is defined by two characteristics: independence and consistency. An independent instruction set does not contain any redundant instructions. That is, each instruction performs a unique function, and does not duplicate the function of another instruction. Also, the opcode/operand relationship is independent and consistent in the sense that any operand can be used with any opcode. Ideally, all operands can equally well be utilized with all the opcodes, and all addressing modes can be consistently used will all operands. Basically, the uniformity offered by an orthogonal instruction set makes the task of compiler development easier. The instruction set should be complete while maintaining a high degree of orthogonality.

<sup>—</sup>Sajjan G. Shiva, Computer Organization, Design, and Architecture, Fourth Edition

The orthogonality of an instruction set is the regularity with which any op-code (without data-size encoding within the opcode itself) can be used with any machineprimitive data-type and addressing mode. The orthogonality of the instruction set makes the architecture easy to learn and program. It reduces the time required to write programs but may result in lower code density. Irregularities adversely affect code-generation efficiency.

# Orthogonal instructions

An instruction set is said to be **orthogonal** if each choice in the building of an instruction is independent of the other choices. Since add and subtract are similar operations, one would expect to be able to use them in similar contexts. If add uses a 3-address format with register addresses, so should subtract, and in neither case should there be any peculiar restrictions on the registers which may be used.

An orthogonal instruction set is easier for the assembly language programmer to learn and easier for the compiler writer to target. The hardware implementation will usually be more efficient too.

## Stephen Byram Furber, "ARM System-on-Chip Architecture"

Повечето съвременни микропроцесори (включително и "ARM") имат висока степен на ортогоналност на системата машинни команди. Но при х86 не е така. Например при 8086 от общо 96 команди ортогонални са само 36. Това се дължи на произхода на този микропроцесор от семейството 8008/8080/8085 с регистъракумулатор (А, превърнал се в AL/AX и регистрови двойки BC, DE и HL, превърнали се в BH:BL, CH:CL и DH:DL при 8086).

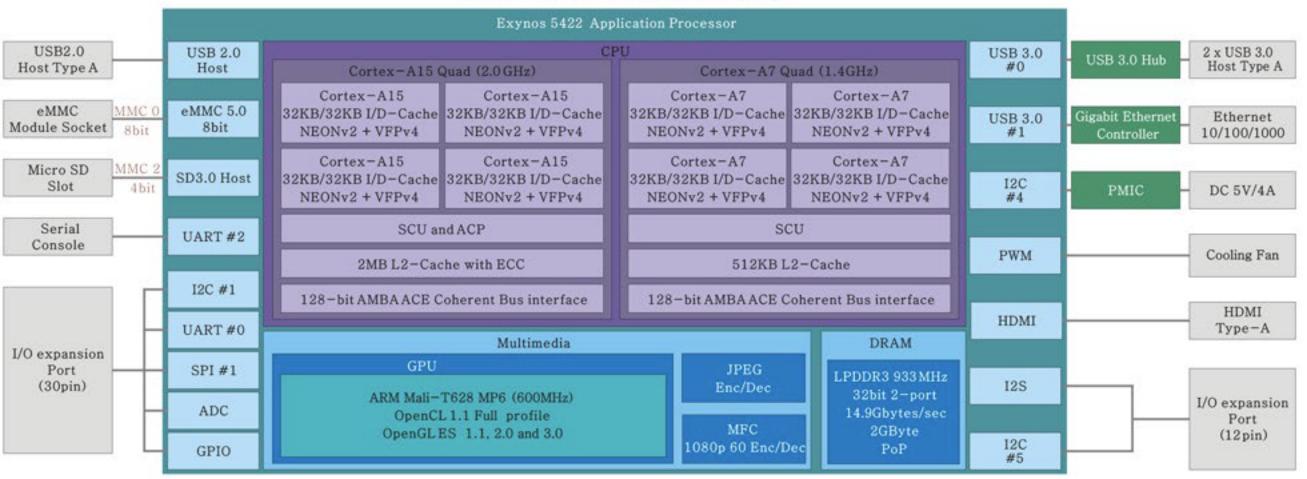

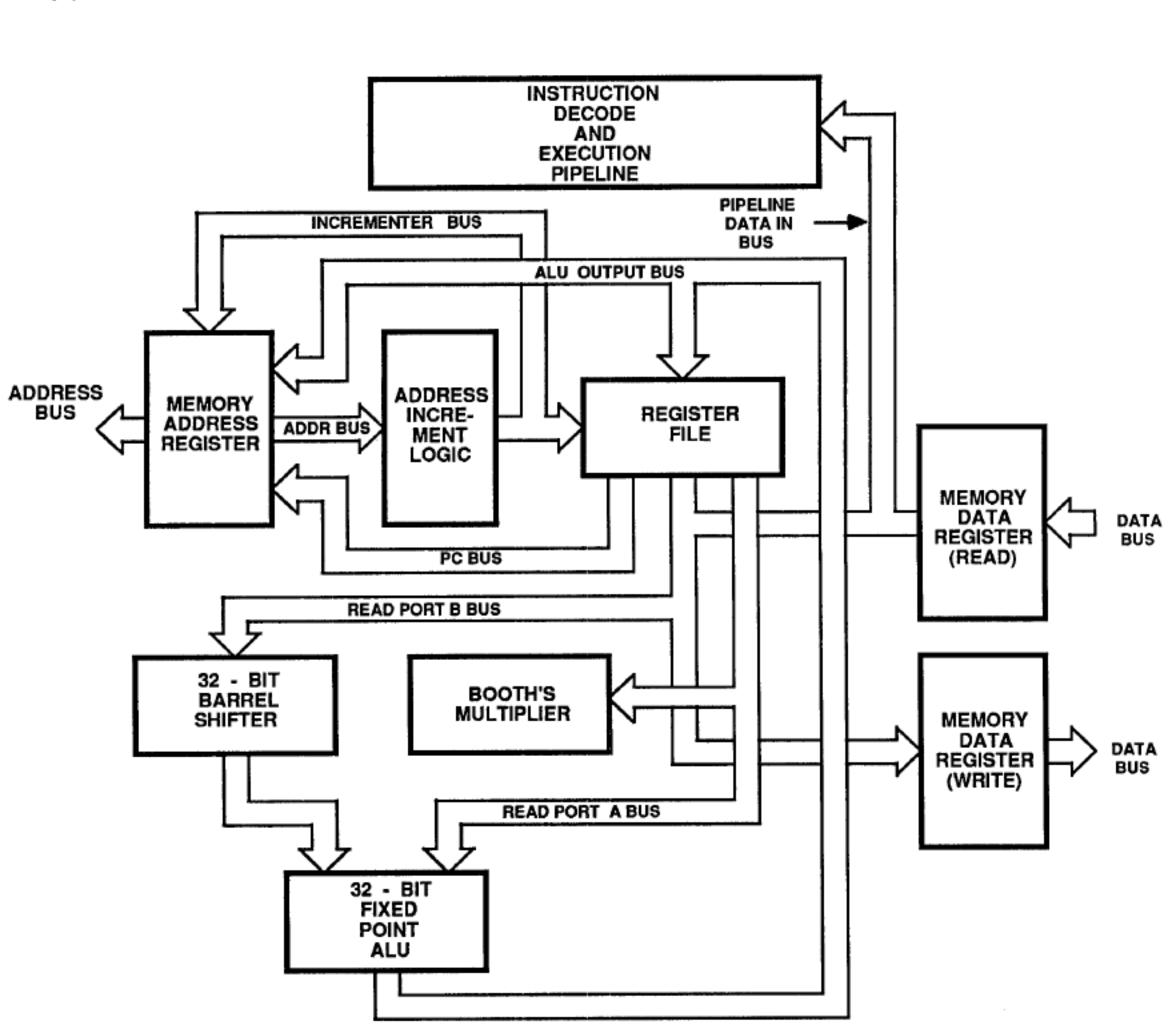

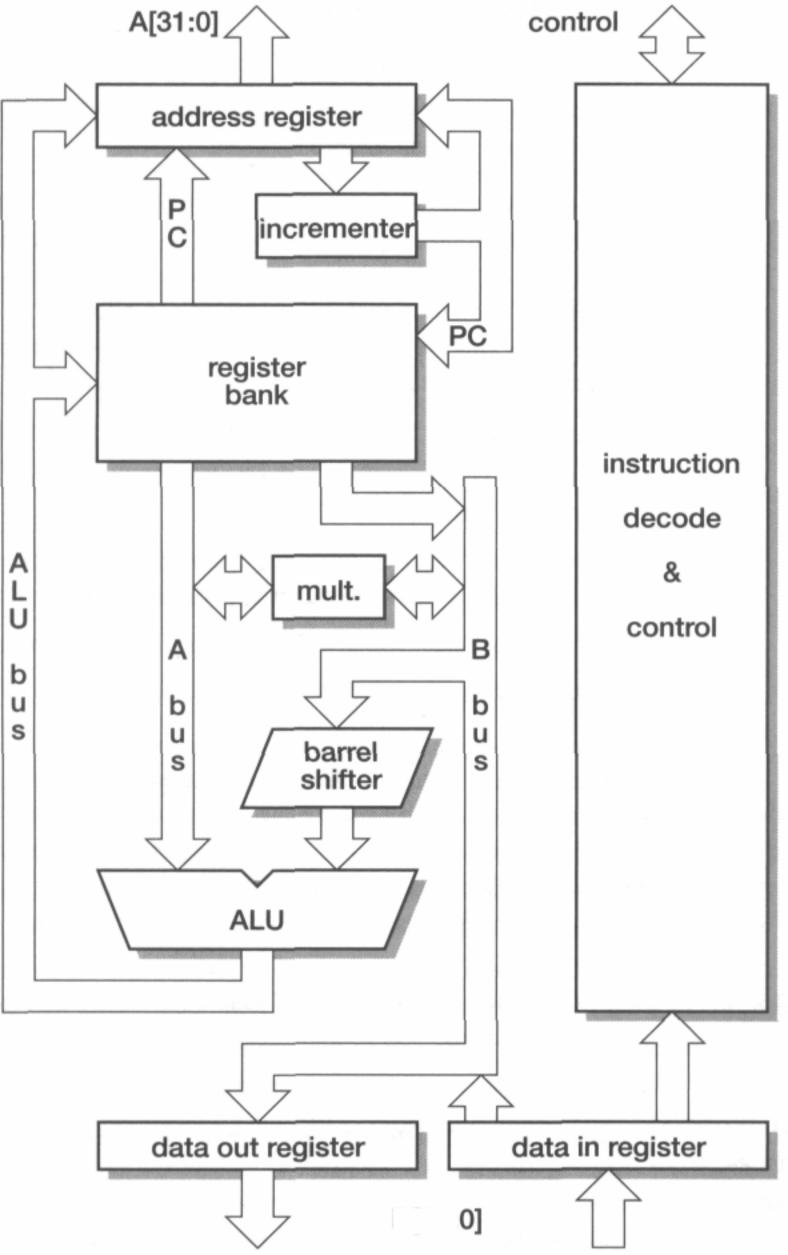

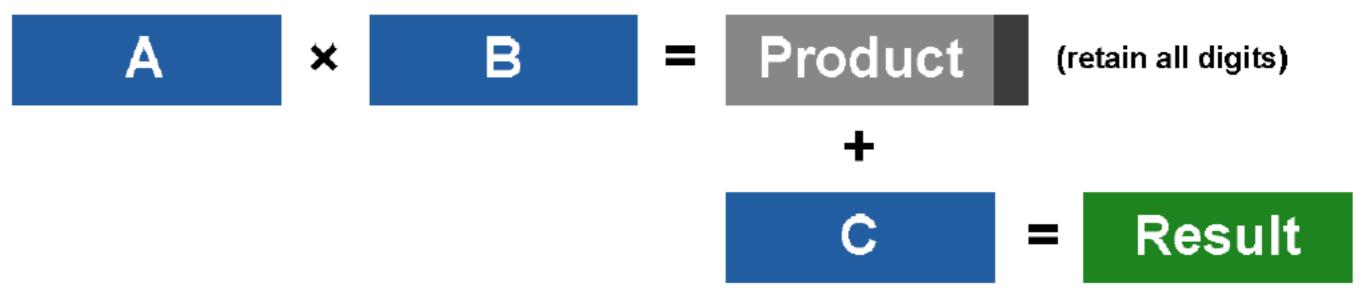

<u>Структура на МП:</u> Основни функционални блокове в МП. Вътрешни шини. Работа на конвейера.

#### ODROID-XU4 BLOCK DIAGRAM

| Instruction<br>Fetch | Instruction<br>Decode | Register<br>Select | Register<br>Read | Shift | ALU  | Register<br>Write |

|----------------------|-----------------------|--------------------|------------------|-------|------|-------------------|

| Fetch                | Dec                   | ode                |                  | Exe   | cute |                   |

### **BLOCK DIAGRAM**

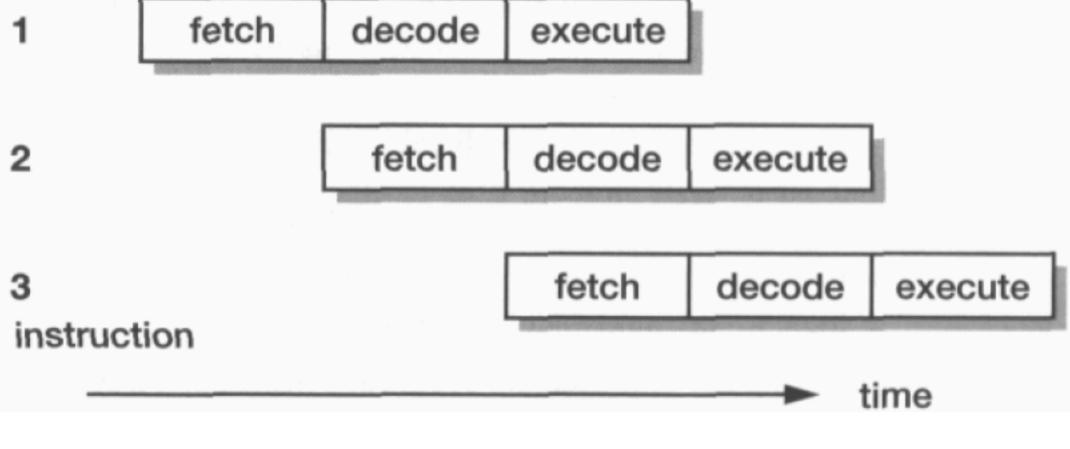

Figure 4.2 ARM single-cycle instruction 3-stage pipeline operation.

Figure 4.3 ARM multi-cycle instruction 3-stage pipeline operation.

| PC | bel | าลง | /iou | ır |

|----|-----|-----|------|----|

|    |     |     |      |    |

gram counter, which is visible to the user as r!5, must run ahead of the current instruction. If, as noted above, instructions fetch the next instruction but one during their first cycle, this suggests that the PC must point eight bytes (two instructions) ahead of the current instruction.

This is, indeed, what happens, and the programmer who attempts to access the PC directly through r!5 must take account of the exposure of the pipeline here. However, for most normal purposes the assembler or compiler handles all the details.

One consequence of the pipelined execution model used on the ARM is that the pro-

for most normal purposes the assembler or compiler handles all the details.

Even more complex behaviour is exposed if r!5 is used later than the first cycle of an instruction, since the instruction will itself have incremented the PC during its first cycle. Such use of the PC is not often beneficial so the ARM architecture definition specifies the result as 'unpredictable' and it should be avoided, especially since later ARMs do not have the same behaviour in these cases.

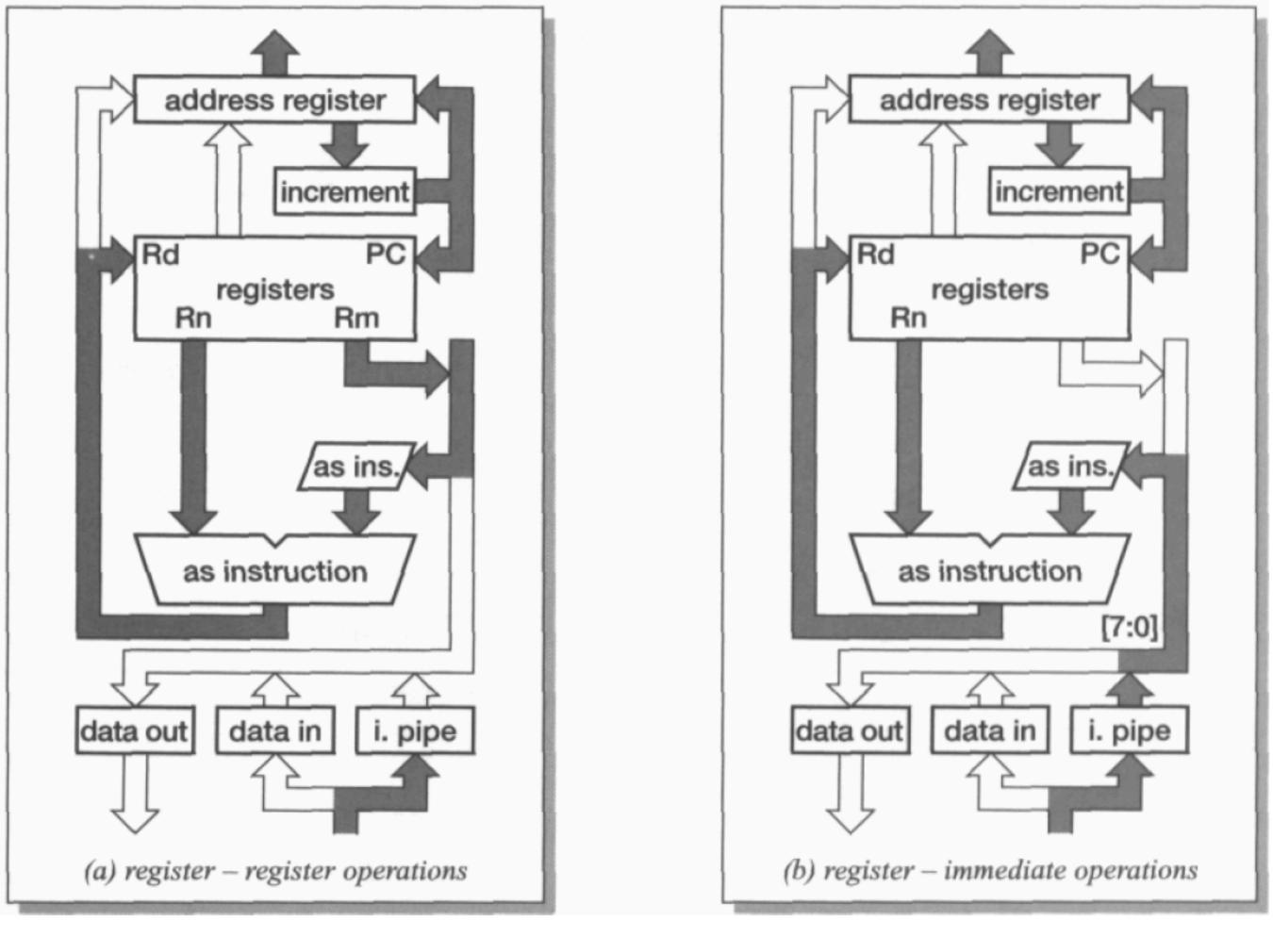

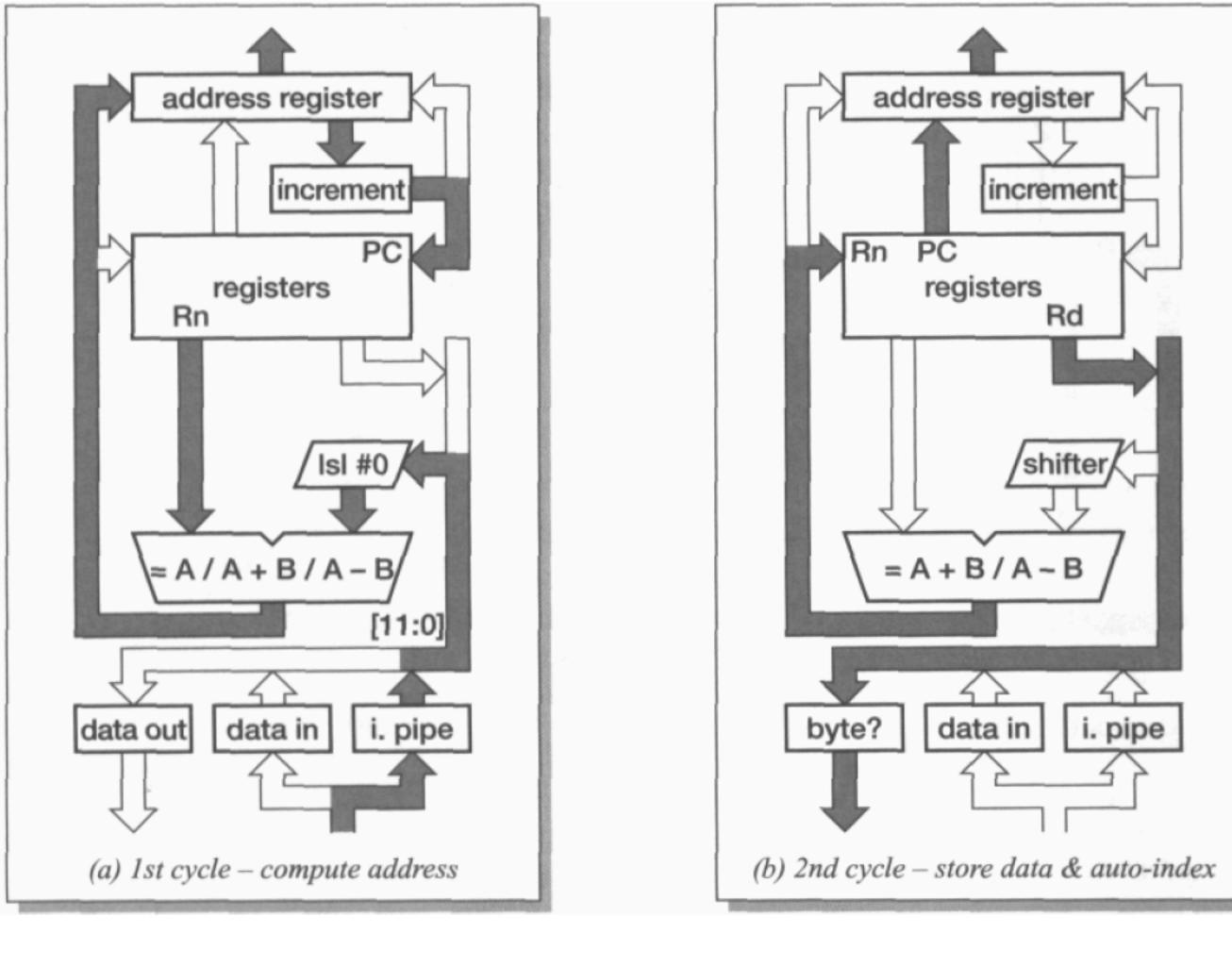

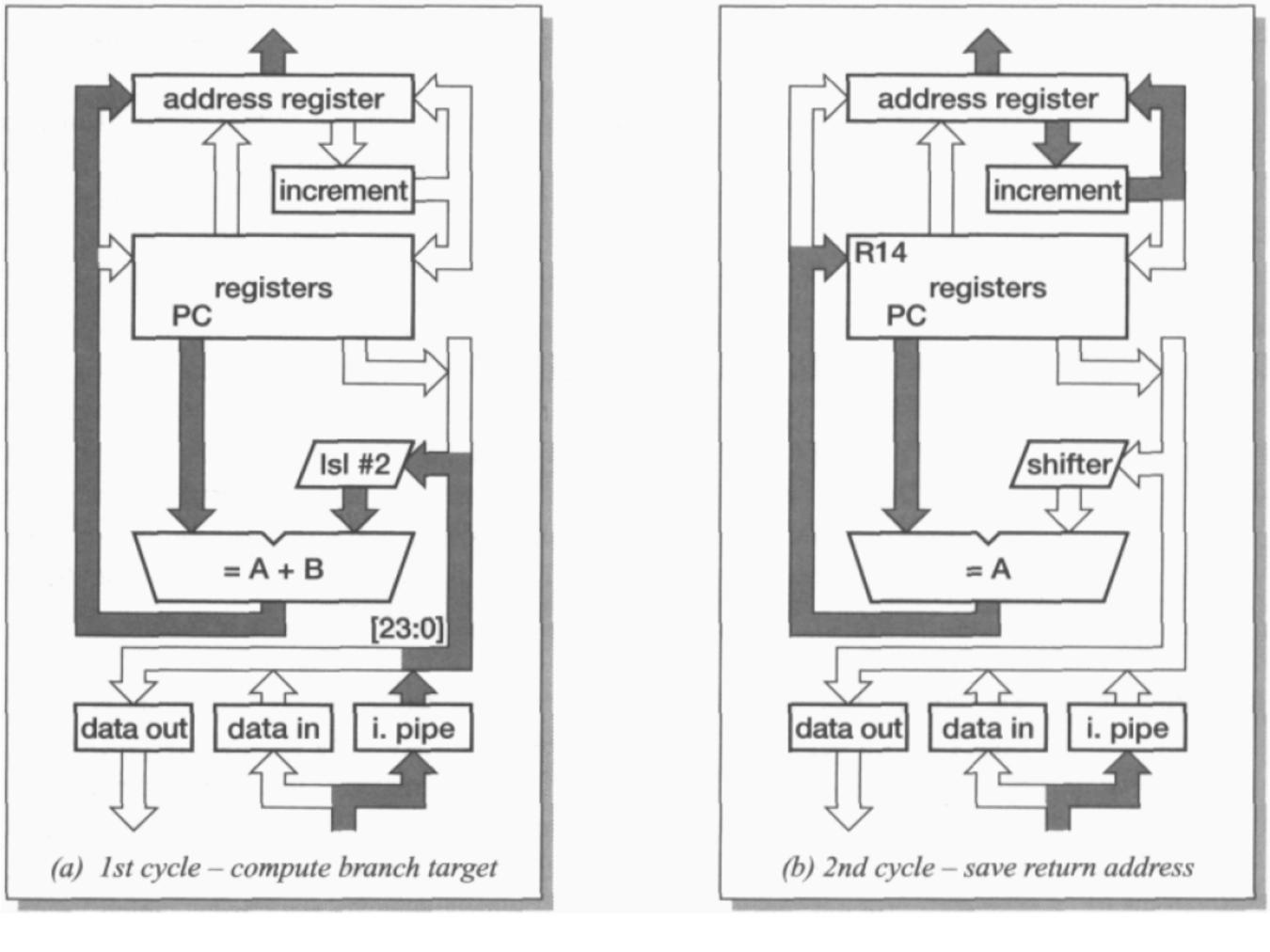

Figure 4.5 Data processing instruction datapath activity.

Figure 4.6 SIR (store register) datapath activity.

Figure 4.7 The first two (of three) cycles of a branch instruction.

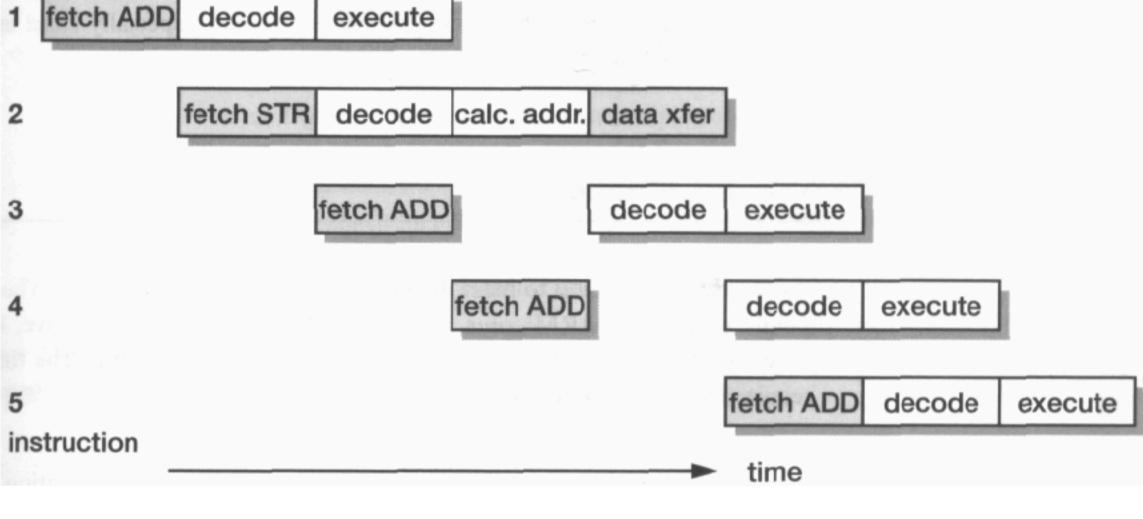

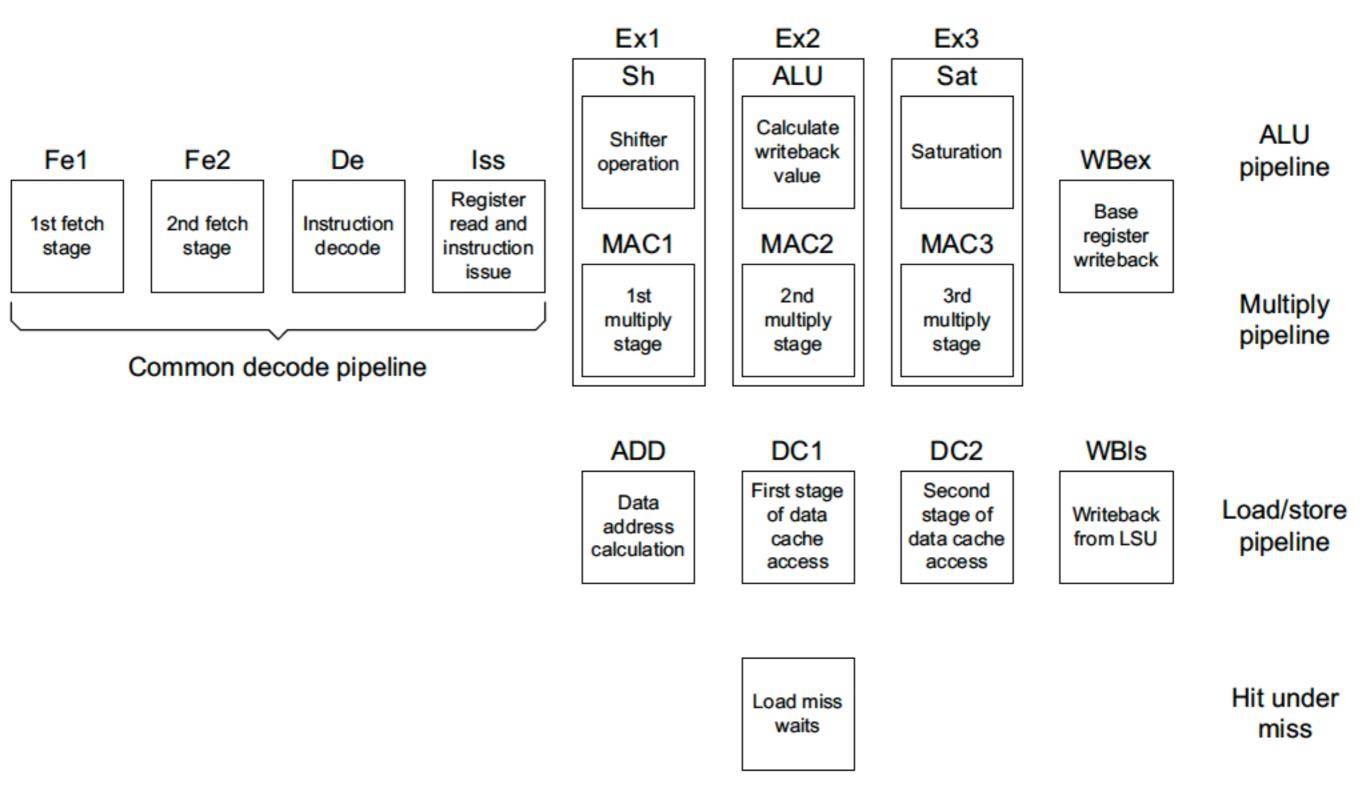

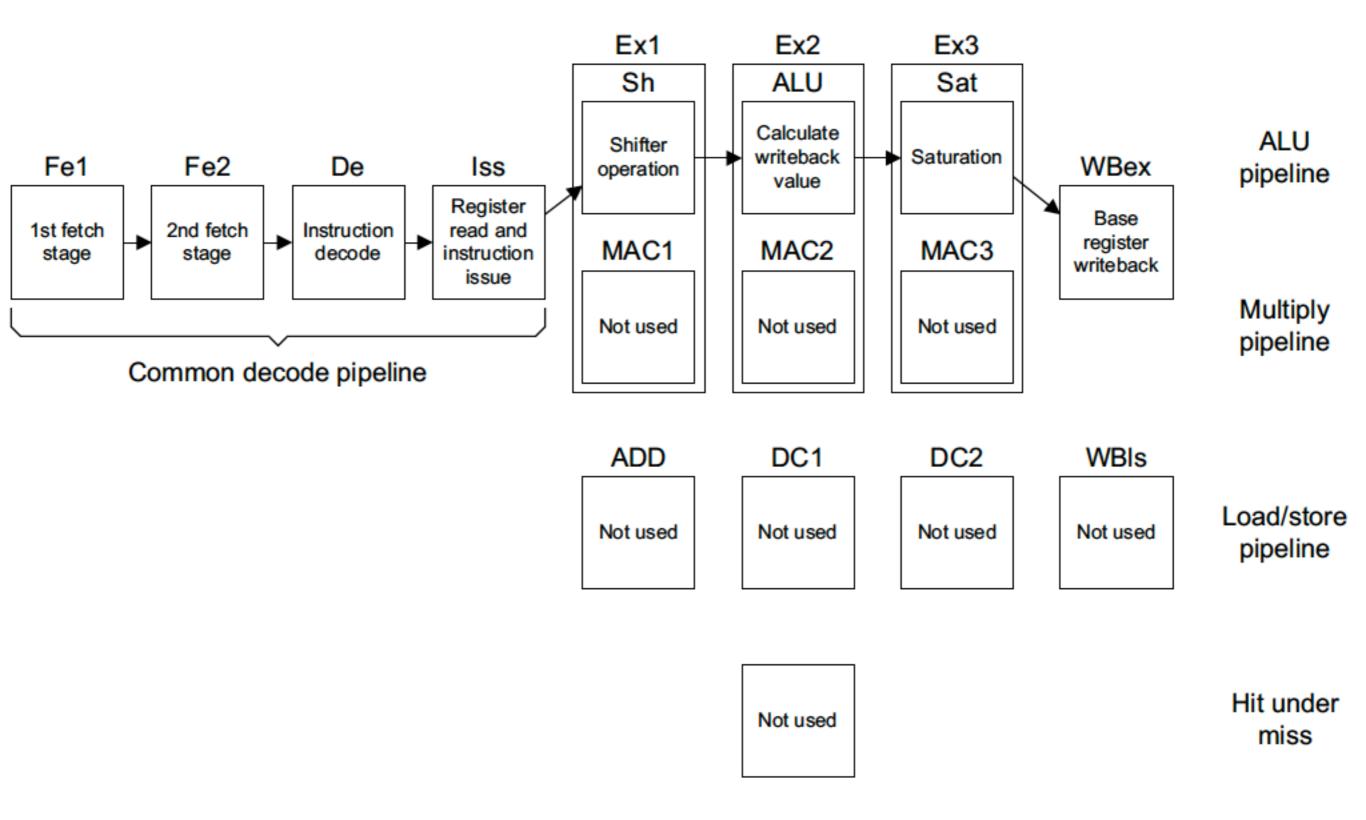

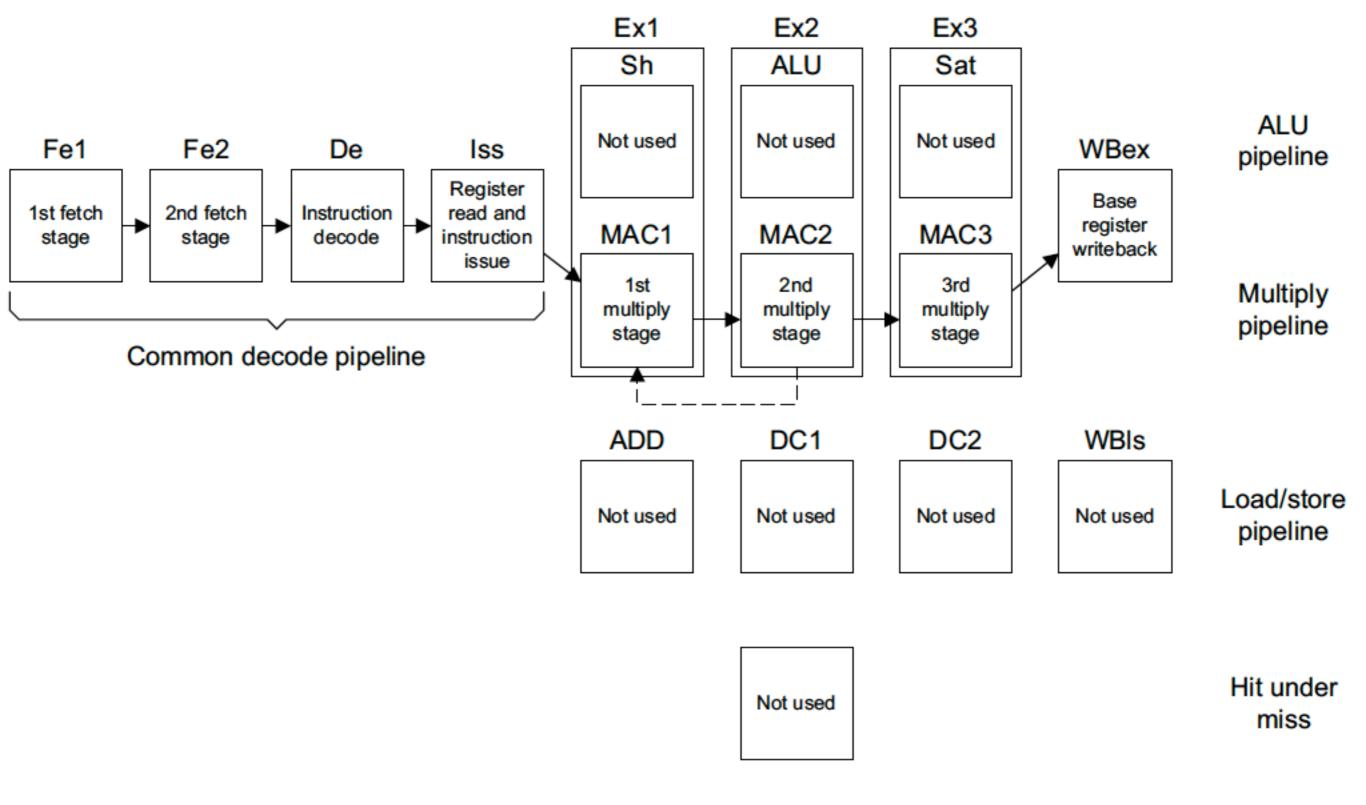

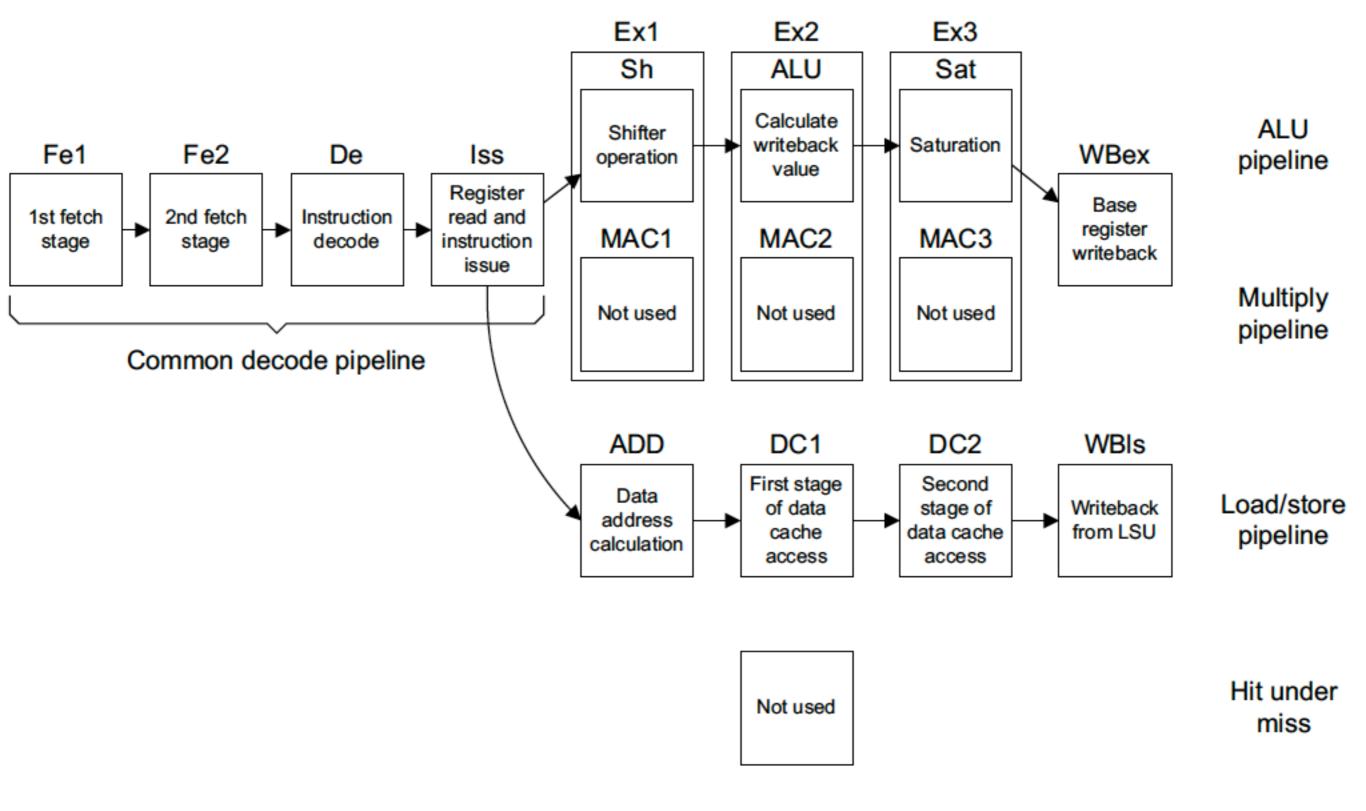

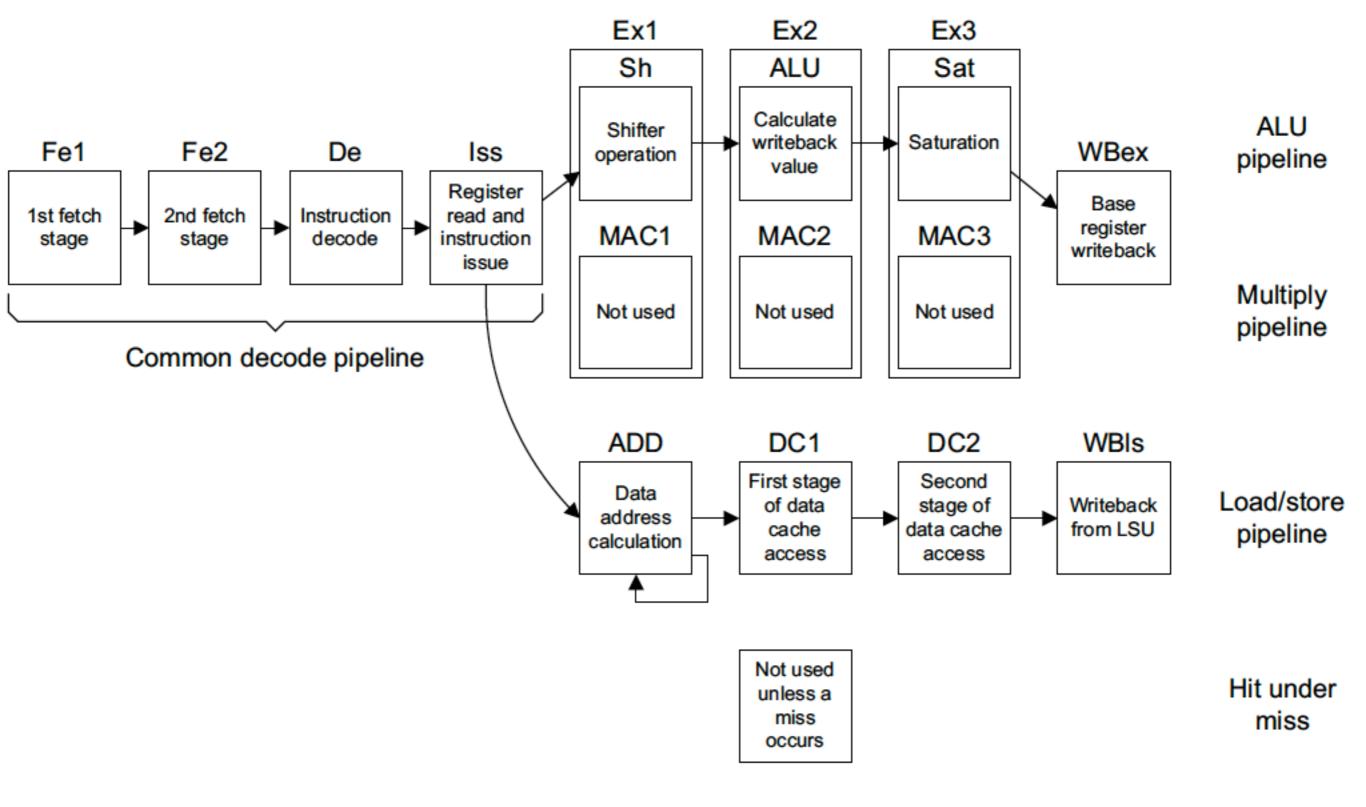

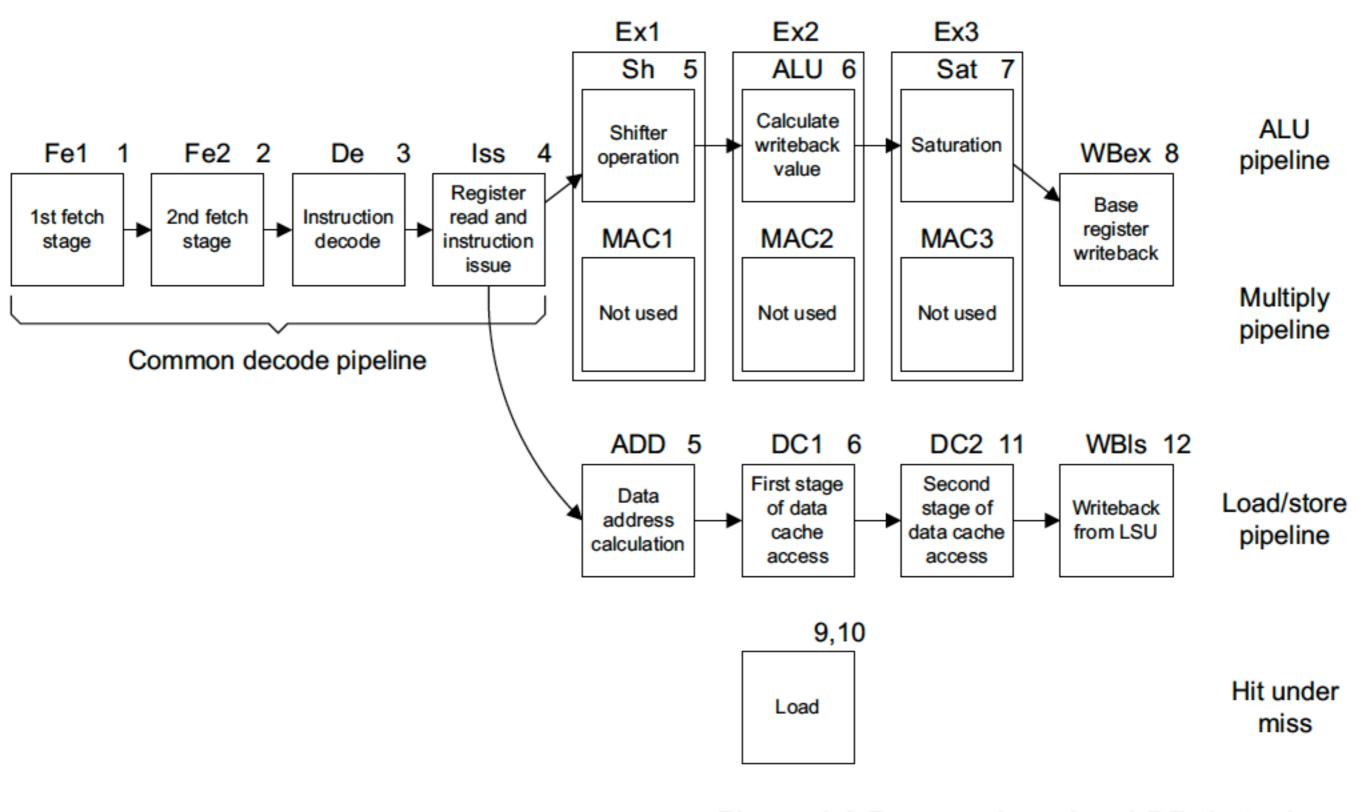

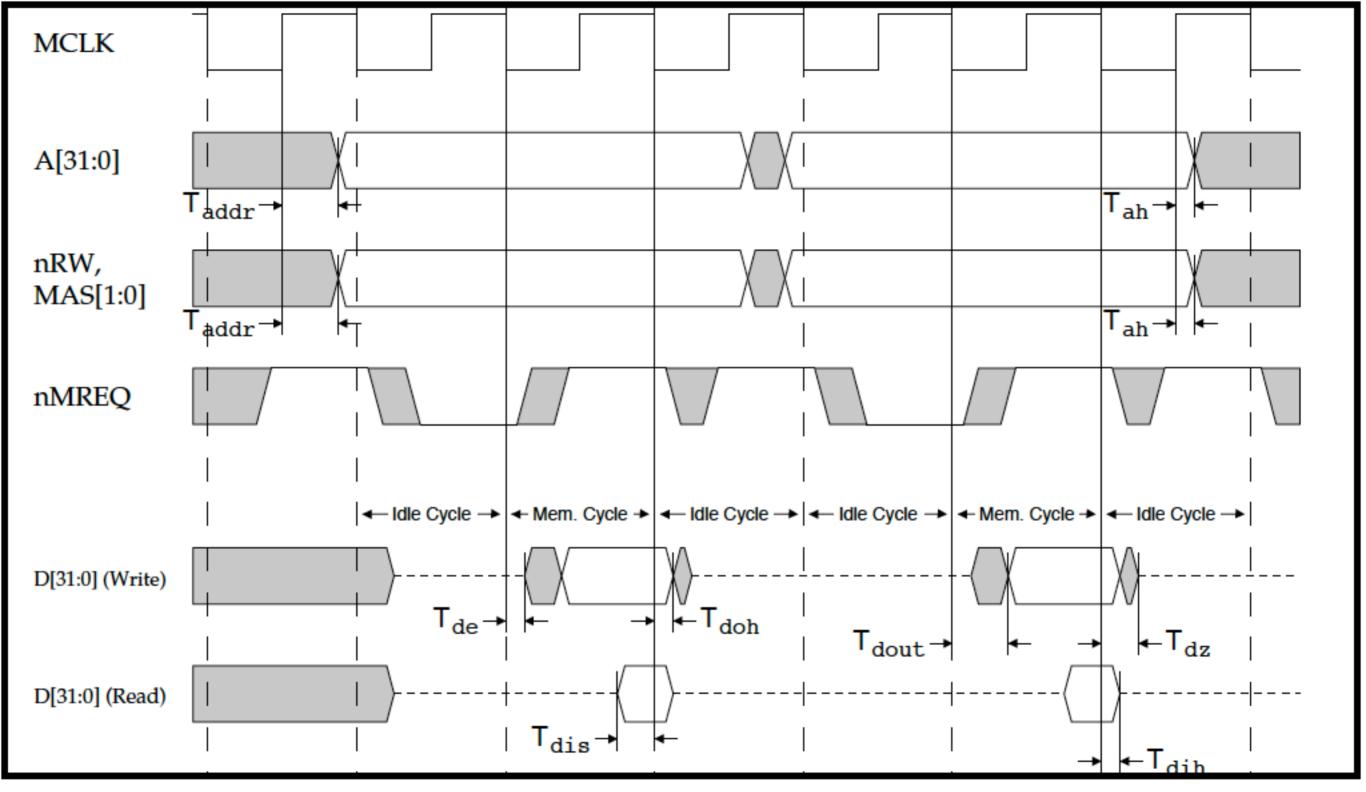

### Figure 1-2 shows:

- the two Fetch stages

- a Decode stage

- an Issue stage

- the four stages of the ARM1176JZF-S integer execution pipeline.

These eight stages make up the processor pipeline.

| Fe1                | Fe2                | De                 | Iss                 | Sh                            | ALU                           | Sat                           | WBex                    |

|--------------------|--------------------|--------------------|---------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------|

| 1st fetch<br>stage | 2nd fetch<br>stage | Instruction decode | Reg. read and issue | Shifter stage                 | ALU operation                 | Saturation stage              | Writeback<br>Mul/ALU    |

|                    |                    |                    |                     | MAC1  1st multiply acc. stage | MAC2  2nd multiply acc. stage | MAC3  3rd multiply acc. stage |                         |

|                    |                    |                    |                     | ADD<br>Address<br>generation  | DC1  Data cache 1             | DC2<br>Data<br>cache 2        | WBls Writeback from LSU |

Figure 1-2 ARM1176JZF-S pipeline stages

| Fe1  | First stage of instruction fetch where address is issued to memory and data returns from memory |

|------|-------------------------------------------------------------------------------------------------|

| Fe2  | Second stage of instruction fetch and branch prediction.                                        |

| De   | Instruction decode.                                                                             |

| Iss  | Register read and instruction issue.                                                            |

| Sh   | Shifter stage.                                                                                  |

| ALU  | Main integer operation calculation.                                                             |

| Sat  | Pipeline stage to enable saturation of integer results.                                         |

| WBex | Write back of data from the multiply or main execution pipelines.                               |

| MAC1 | First stage of the multiply-accumulate pipeline.                                                |

| MAC2 | Second stage of the multiply-accumulate pipeline.                                               |

| MAC3 | Third stage of the multiply-accumulate pipeline.                                                |

| ADD  | Address generation stage.                                                                       |

| DC1  | First stage of data cache access.                                                               |

| DC2  | Second stage of data cache access.                                                              |

| WBls | Write back of data from the Load Store Unit.                                                    |

Figure 1-3 Typical operations in pipeline stages

Figure 1-4 Typical ALU operation

Figure 1-5 Typical multiply operation

Figure 1-6 Progression of an LDR/STR operation

Figure 1-7 Progression of an LDM/STM operation

Figure 1-8 Progression of an LDR that misses

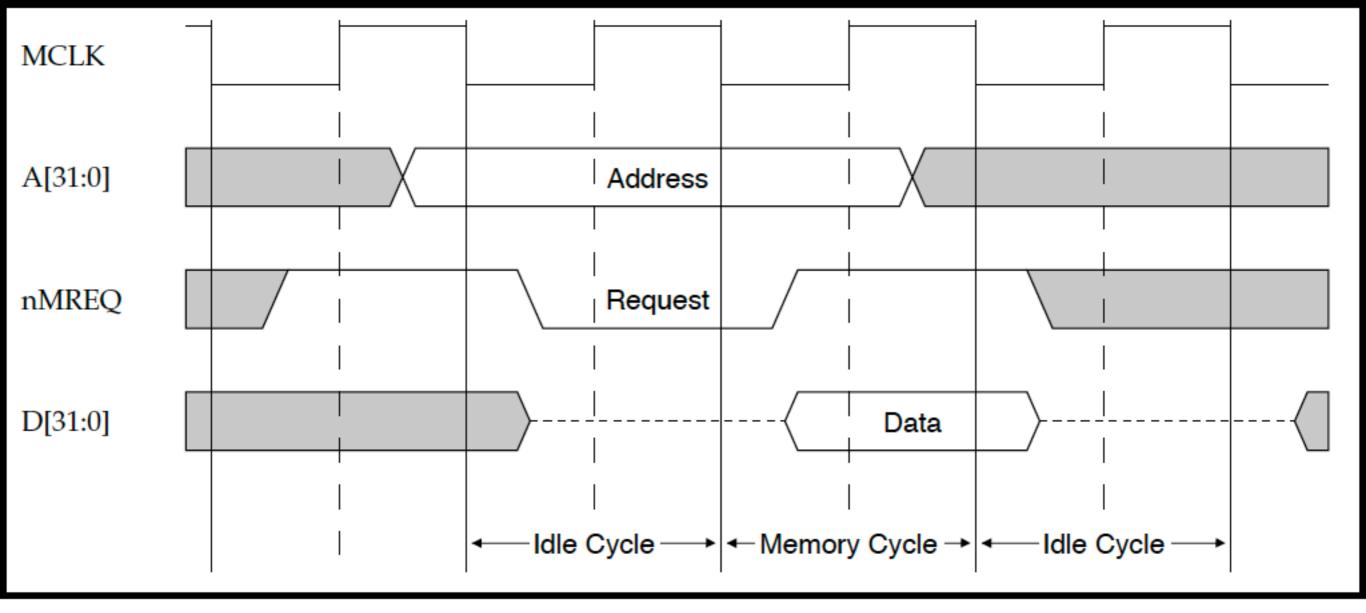

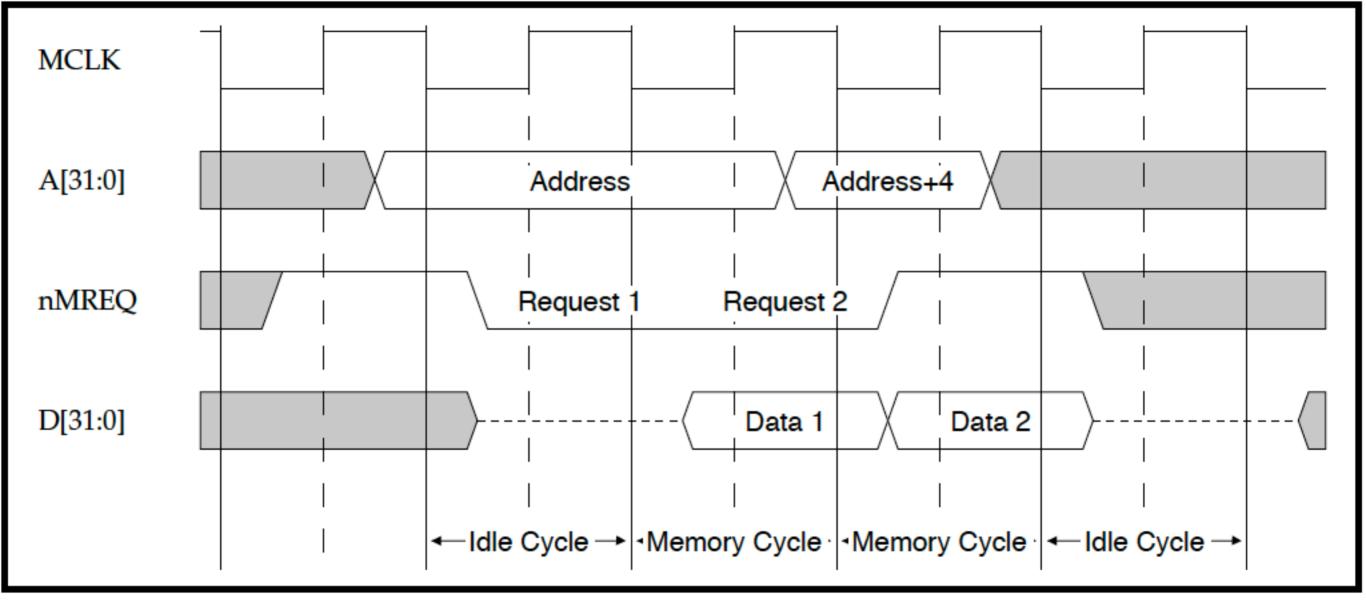

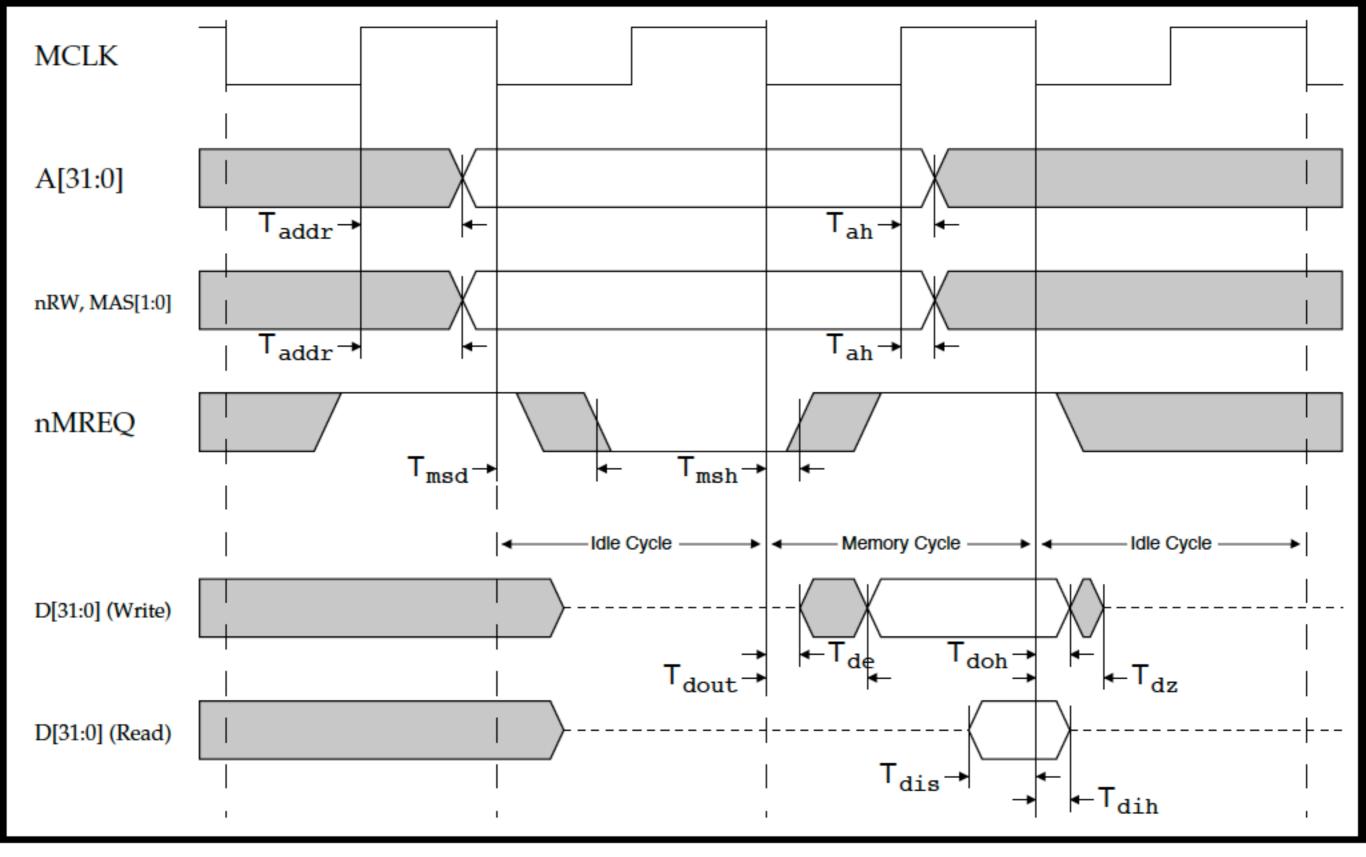

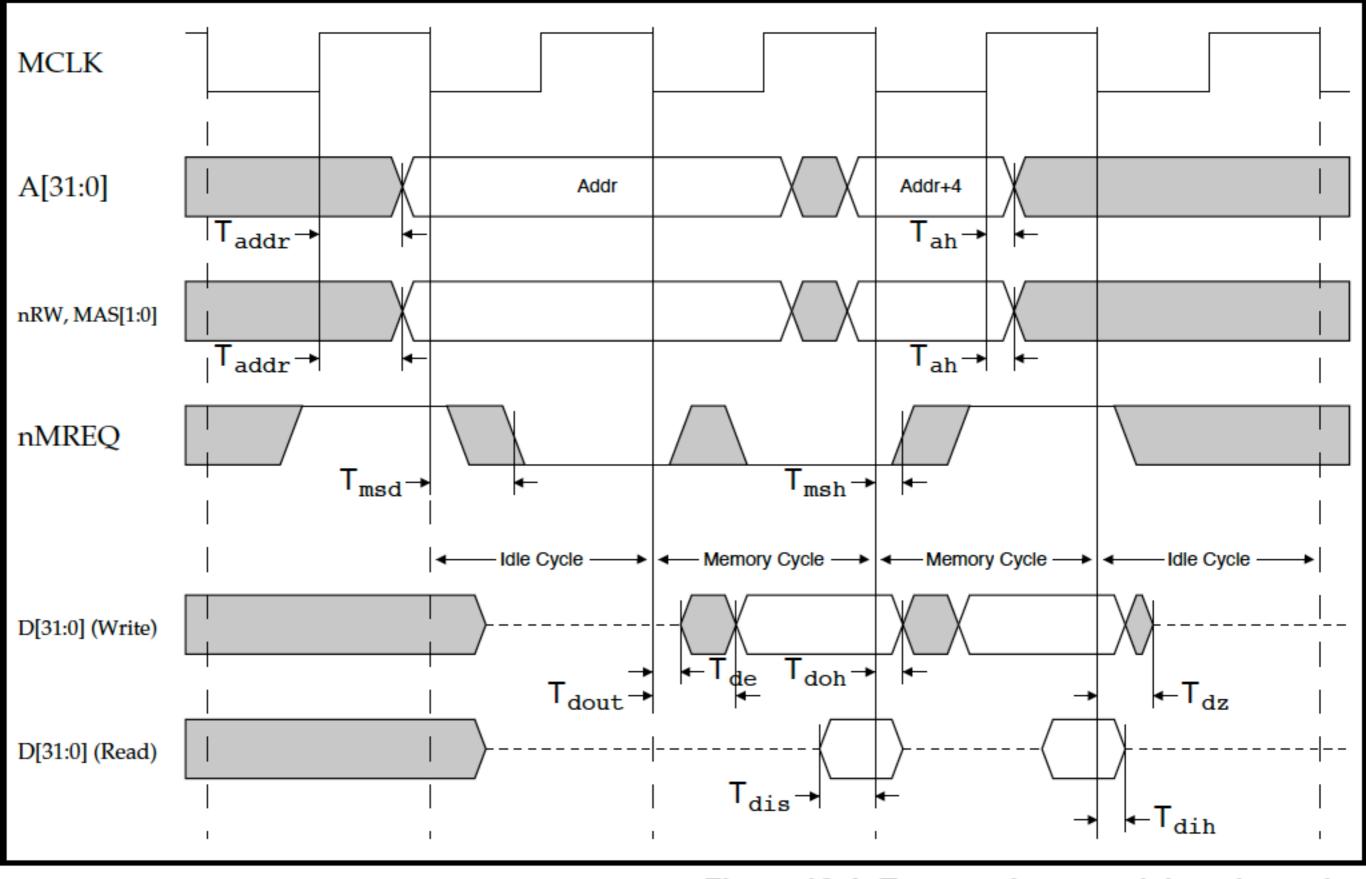

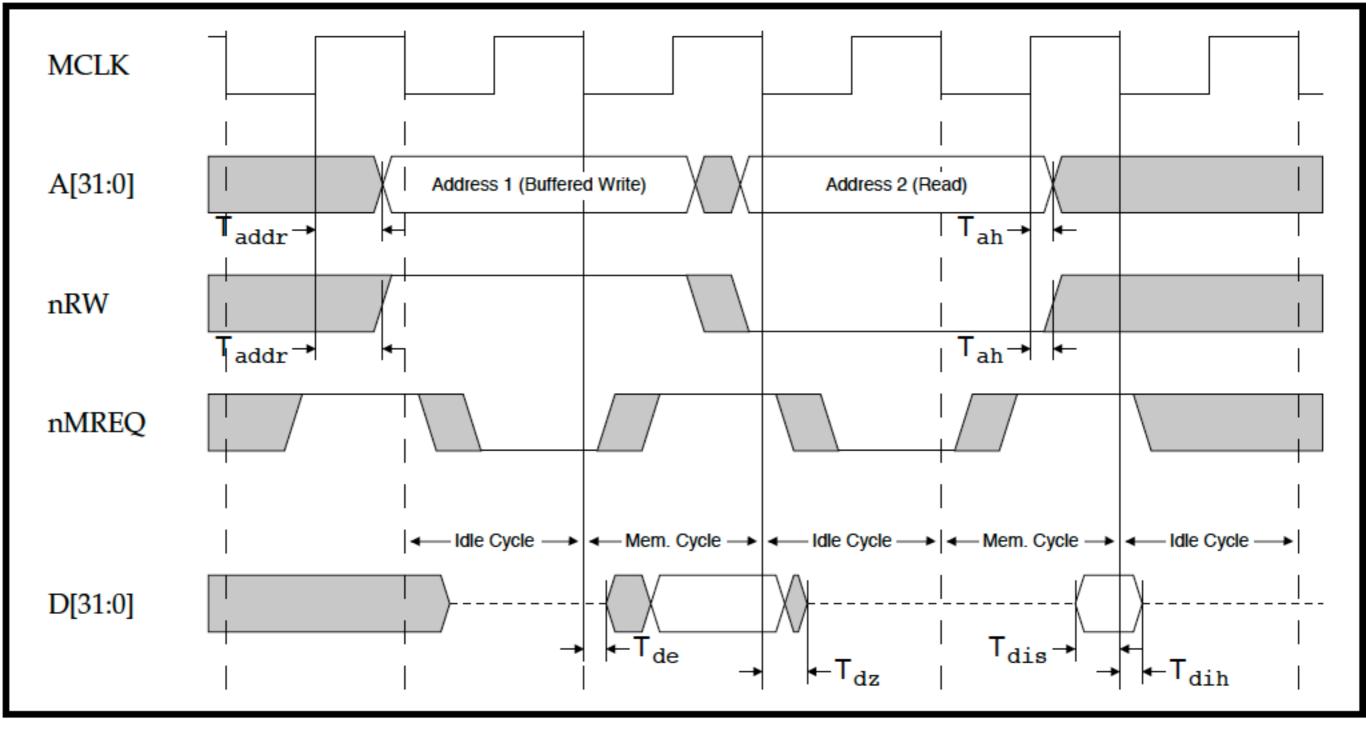

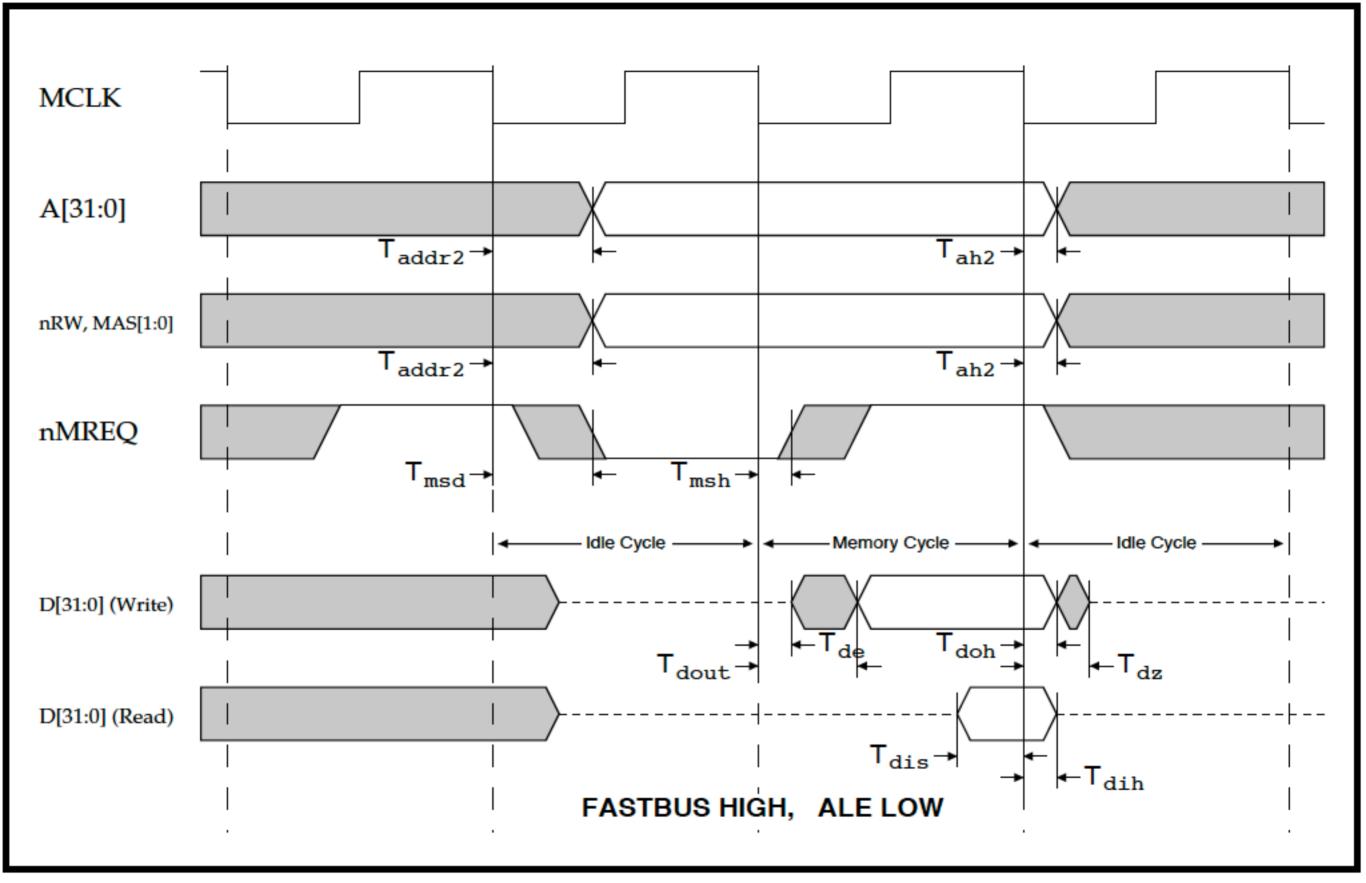

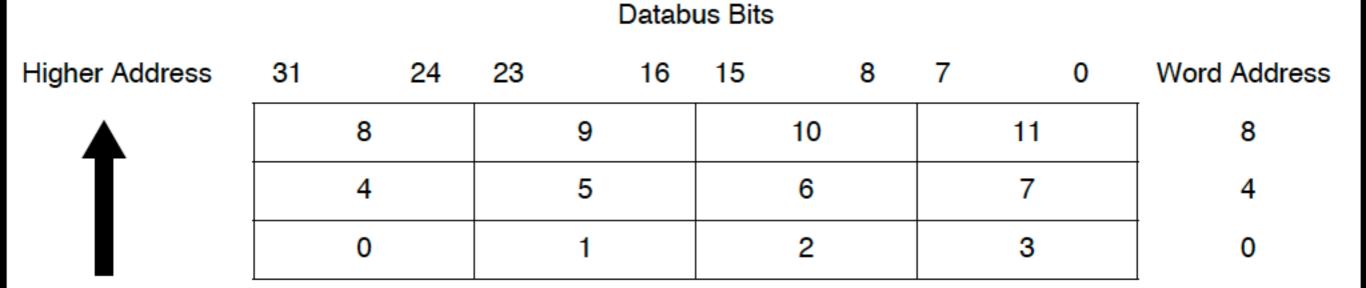

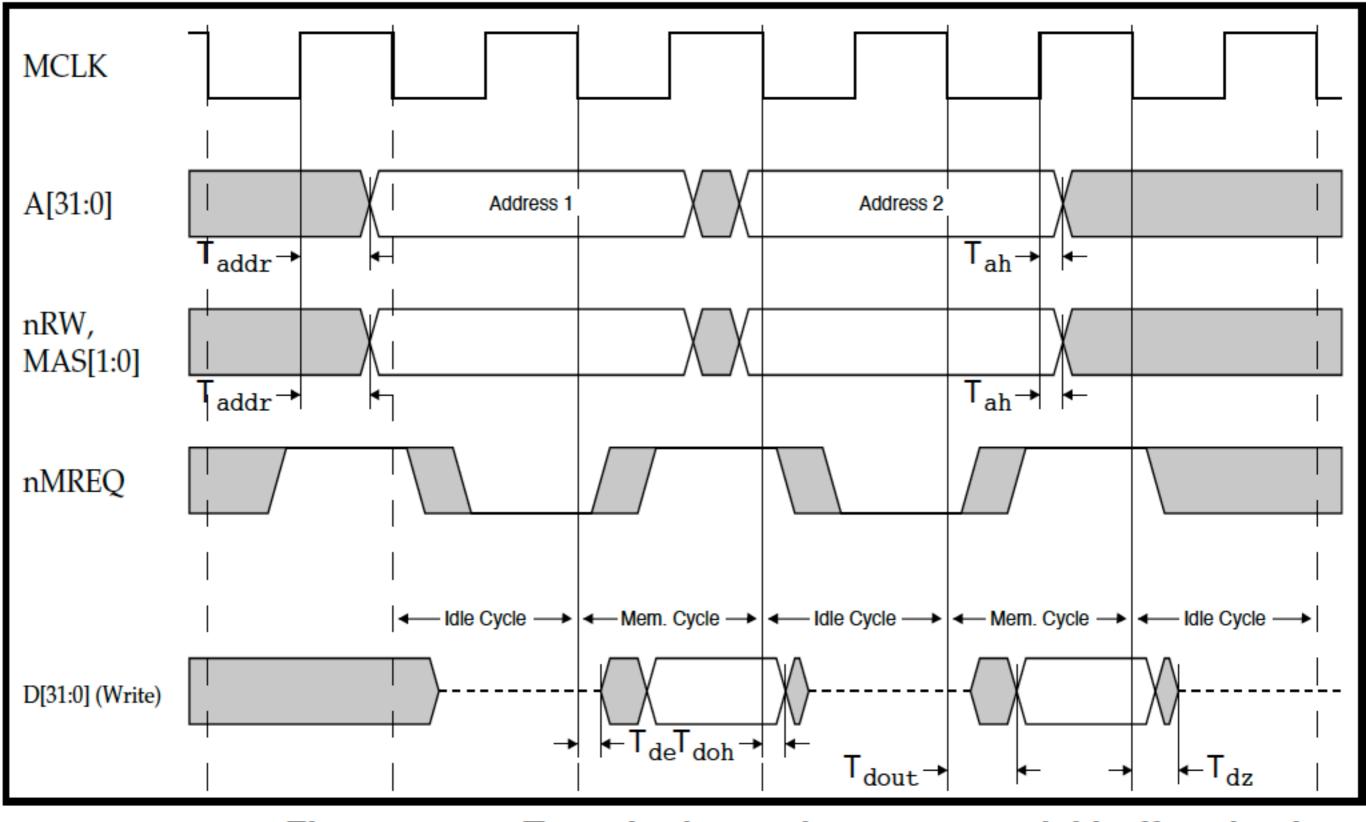

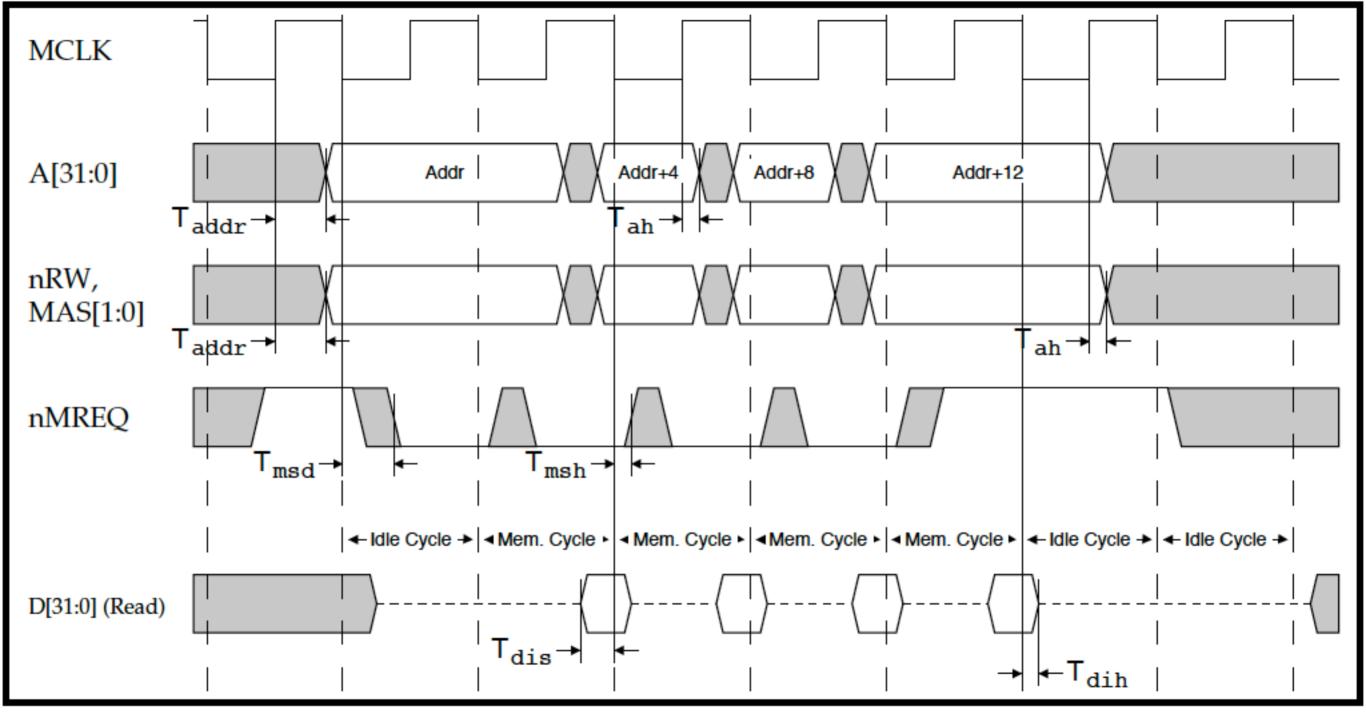

| Системна магистрала: Сигнали на шините за адреси и данни. Управляващи сигнали. Организация на обмена на данни. Видове цикли. Времедиаграми. |

|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                             |

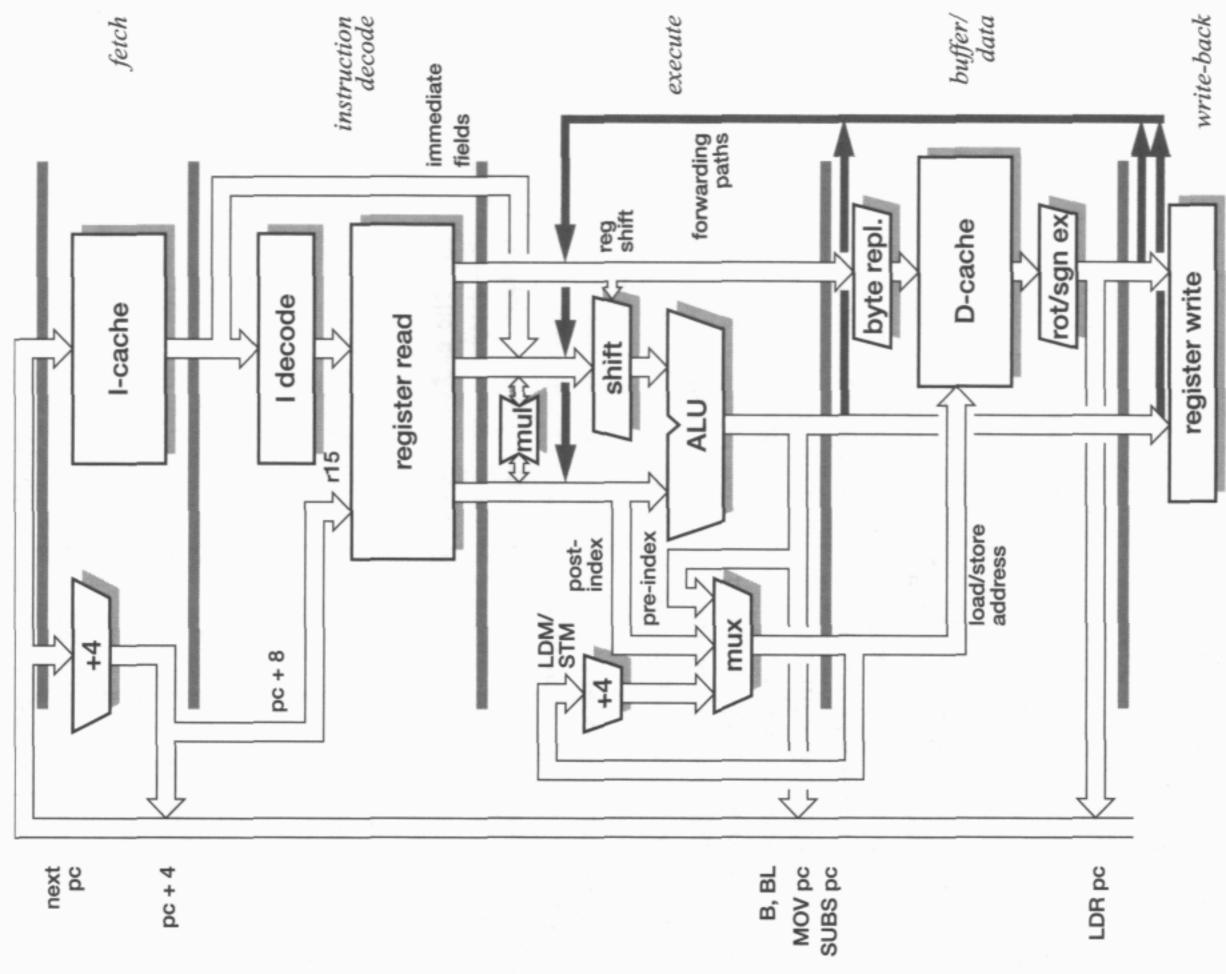

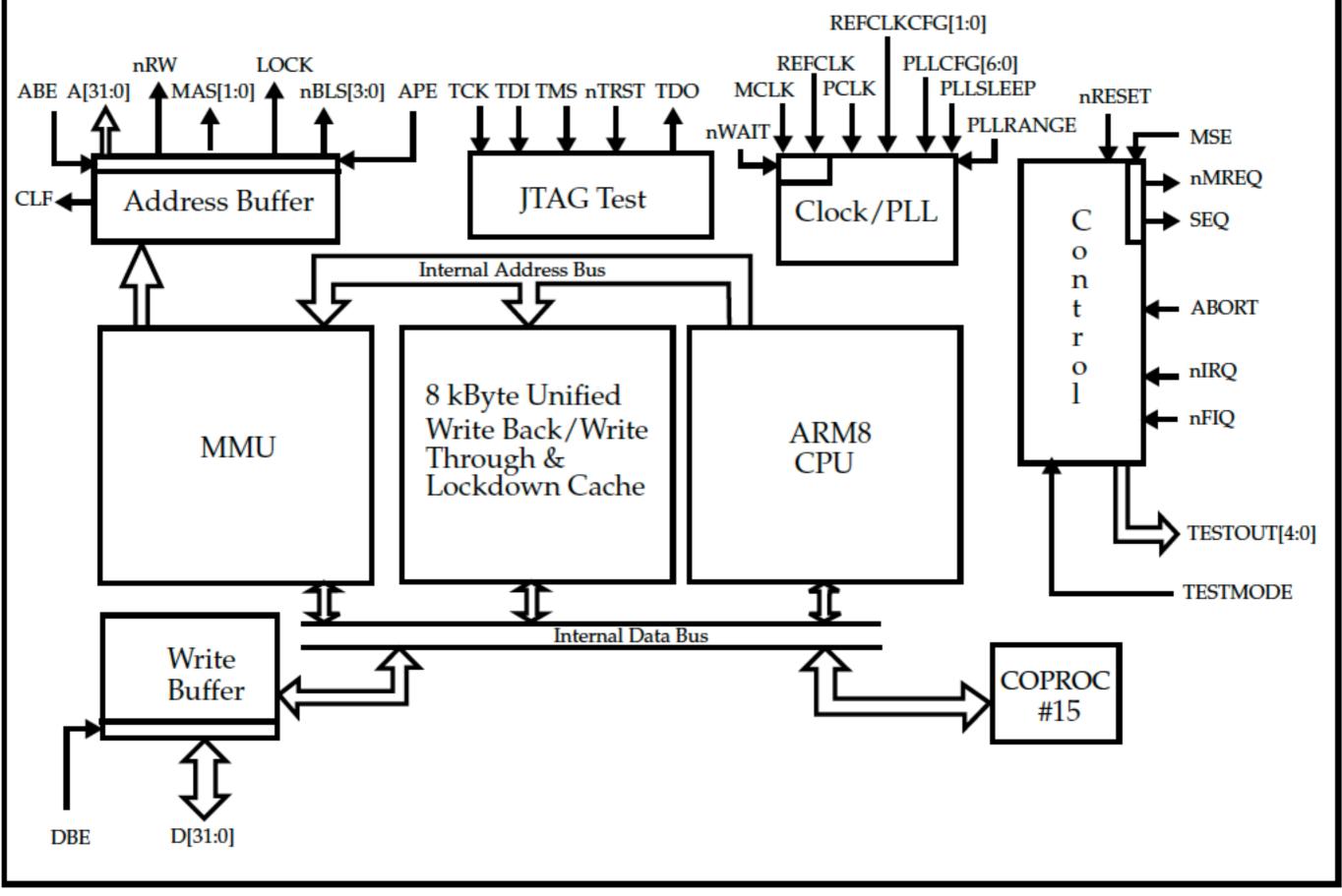

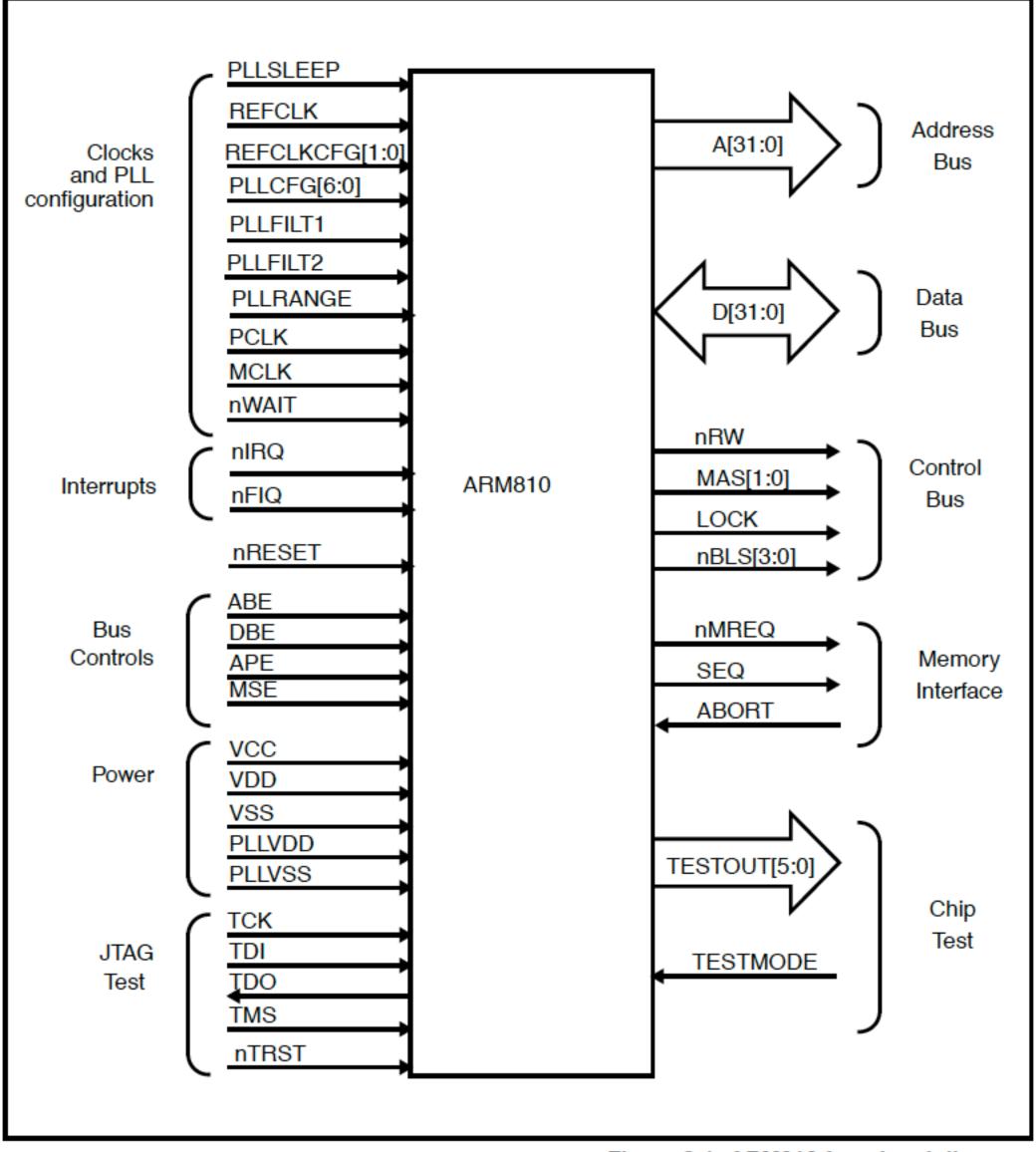

Figure 1-1: ARM810 block diagram

Figure 2-1: ARM810 functional diagram

# Key to signal types:

Input Output, CMOS levels, tristateable OCZ*IOCZ* Input/output tristateable, CMOS levels Clock input ICK

| A[31:0] | OCZ | Address Bus. This bus signals the address requested for memory accesses. Normally it changes during phase 2 of the bus clock. The timing can be changed using <b>APE</b> .                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABE     | I   | Address bus enable. When this input is LOW, the address bus A[31:0], MAS[1:0], CLF, nBLS[3:0], nRW and LOCK are put into a high impedance state (Note 1).                                                                                                                                                                                                                                                                                                                                                                                                        |

| ABORT   | I   | External abort. Allows the memory system to tell the processor that a requested access has failed. Only monitored when ARM810 is accessing external memory.                                                                                                                                                                                                                                                                                                                                                                                                      |

| APE     |     | Address pipeline enable control input. When APE is HIGH, address and address-timed outputs are generated with normal pipeliined timing, where a new address is generated in the second phase of the bus clock (MCLK HIGH or PCLK LOW). Taking APE LOW delays these signals by one clock phase so they change in the first phase of the following bus cycle (MCLK LOW or PCLK HIGH). See the descriptions for MCLK/PCLK and Chapter 11, ARM810 Clocking for bus clock information. The address-timed signals are A[31:0], MAS[1:0], nBLS[3:0], CLF, LOCK and nRW. |

| CLF     | 0   | Cache line fill. <b>CLF</b> HIGH indicates that the current read cycle is cacheable. <b>CLF</b> is always HIGH for writes. This signal may be used to indicate to a second level cache controller that a read is cacheable in the second level cache (if present).                                                                                                                                                                                                                                                                                               |

| D[31:0] | IOCZ | Data bus. These are bi-directional signal paths used for data transfers between the processor and external memory. For read operations (when <b>nRW</b> is LOW), the input data must be valid before the falling edge of <b>MCLK</b> . For write operations (when <b>nRW</b> is HIGH), the output data will become valid while <b>MCLK</b> is LOW. At high clock frequencies the data may not become valid until just after the <b>MCLK</b> rising edge. |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBE     | I    | Data bus enable. When this input is LOW, the data bus, <b>D[31:0]</b> is put into a high impedance state (Note 1). The drivers will always be high impedance except during write operations, and <b>DBE</b> must be driven HIGH in systems which do not require the data bus for DMA or similar activities.                                                                                                                                              |

| LOCK    | OCZ  | Locked operation. <b>LOCK</b> is driven HIGH, to signal a "locked" memory access sequence, and the memory manager should wait until <b>LOCK</b> goes LOW before allowing another device to access the memory. <b>LOCK</b> remains HIGH during the locked memory sequence. Normally it changes during phase 2 of the bus clock. The timing can be changed using <b>APE</b> .                                                                              |

| MCLK    |      | This is a bus clock input. Bus cycles start and end with falling edges of MCLK. Hold PCLK HIGH to use this clock input. See 11.1.1 External input clock: MCLK or PCLK on page 11-3 for further details. This signal is provided for backwards compatibility with previous processors, see PCLK for the preferred bus clock input.                                                                                                                        |

| MSE       | I   | Memory request/sequential enable. When this input is LOW, the <b>nMREQ</b> and <b>SEQ</b> outputs are put into a high impedance state (Note 1).                                                                                                                                                                                                        |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAS[1:0]  | OCZ | Memory Access Size. An output bus used by the processor to indicate the size of the next data transfer to the external memory system as being a byte, half word or full 32 bit word in length. MAS[1:0] is valid for both read and write operations. Normally it changes during phase 2 of the bus clock. The timing can be changed using <b>APE</b> . |

| nBLS[3:0] | OCZ | Not Byte Lane Selects. These signify which bytes of the memory are being accessed. For a word access all will be LOW. Normally they change during phase 2 of the bus clock. The timing can be changed using <b>APE</b> .                                                                                                                               |